VLSI Test Lab

As digital and analog circuits become ever more complex with higher levels of device integration, new techniques must be developed in order to manufacture devices at reasonable costs. Modern devices are prone to manufacturing defects as a consequence of small device sizes. To prevent the catastrophic consequences of a defective device’s use, all devices must be thoroughly tested be they are delivered to the customer. This be done in an efficient manner, otherwise testing will impact device manufacturing costs.Future Projects

Artificial Neural Networks for Random Pattern Testing

The use of pseudo-random patterns has been document to be cost-effective for detecting defects in previous generations of technologies. As circuits have become more complex, pseudo-random patterns are losing their effectiveness, but alternative strategies have not compensated for this loss.

Artificial neural networks (ANNs) have recently been demonstrated to be a viable means to solving previously unsolvable problems. As computational resources have become more powerful and data has become more available, ANNs have transitioned from a technological curiosity to an implementable solution. This is especially true for problems where an optimal answer is not necessary required, but current methods of providing an answer are inaccurate or infeasible to calculate.

ANNs lave potential to solve many problems of pseudo-random testing, especially those which have become infeasible to solve from increasing circuit sizes. This lab will perform experiments in applying ANNs to these problems and observing the quality of solutions obtained against existing methods. Potential applications of ANNs include the following.

- Minimizing hardware overhead and maximizing the effectiveness of test point insertion.

- Optimizing weighted random patterns for increasing circuit fault coverage.

- Maximizing the detection of delay faults using pseudo-random pattern testing.

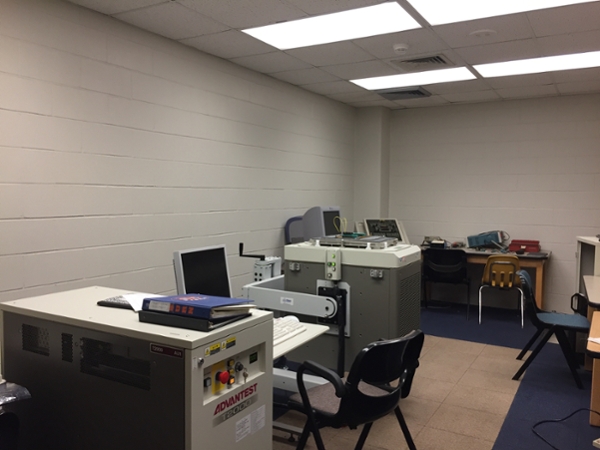

Equipment

Computing resources

The VLSI Test Lab possesses several high-performance work stations for the purpose of algorithm development and data management. These workstations are connected to Auburn University’s high-performance computing clusters, CASIC and HOPPER.

Advantest T2000 ATE

The VLSI Test Lab houses an Advantest T2000 automated test equipment (ATE). This machine has the ability to simultaneously probe and stimulate 256 pins at a rate of 200 MHz. The machine also has the ability to apply the same pattern over varying power supply (voltage) and chip speed (specifications) to find a point of failure. In this lab, this equipment can be used with a FPGA to emulate a (defective) chip.