# **Chapter 15**

# **BUILT-IN SELF-TEST**

"In a digital instrument designed for troubleshooting by signature analysis, this method can find the components responsible for well over 99% of all failures, even intermittent ones, without removing circuit boards from the instrument."

— Robert A. Frohwerk, in "Signature Analysis: A New Digital Field Service Method" [228].

Frohwerk ushered in a new era of determining the correctness of a circuit by examining a signature, which is some statistical property of the circuit. He applied the work of Peterson and Weldon [521] and Golomb [264] on error-correcting codes and shift register sequences to built-in self-testing (BIST) of ICs. Frohwerk also provided the first analysis for transition count testing and BIST to determine the probability of a signature indicating the circuit was good, when in fact it was faulty.

A digital system is tested and diagnosed during its lifetime on numerous occasions. Test and diagnosis must be quick and have very high fault coverage. One way to ensure this is to specify test as one of the system functions, so it becomes self-test. At the highest level of systems test, the testing function is frequently implemented in software. Many digital systems designed at AT&T circa 1987 had self-test, usually implemented in software [33]. Its most common use was in maintenance and repair diagnostics. Although this approach provided flexibility, it also had disadvantages. The fault coverage and the diagnostic resolution of those software-implemented tests were not as high as desired. The diagnostic resolution may be poor because the software must test parts that are difficult to test, and therefore it may not effectively determine which part is at fault. Also, software tests can be long, slow, and expensive to develop. Therefore, it becomes increasingly attractive to build the self-test function into the hardware [36, 37]. It is also most effective to consider testing as early in the design cycle as possible. Otherwise, costly prototyping turns (cycles of redesign and refabrication of the prototype) result, and these lead to schedule slippages for product introduction.

Systems designed without an integrated test strategy (covering all levels from the entire system to components) can best be described as *chip-wise and system-foolish*. With properly designed BIST, the cost of added test hardware will be more than balanced by the benefits in terms of reliability and the reduced maintenance cost [33].

Thus, these benefits, rather than the cost, can be passed on to the customers. The savings from BIST include reduced test generation effort at all levels, reduced test effort at chip through system levels, improved system-level maintenance and repair, and improved component repair. Gordon and Nadig [266] described the economic impact of signature analysis and BIST on the first systems that used BIST: two Hewlett-Packard digital voltmeters, one of them called the HP 3455A. Development time and costs rose roughly 1%. There was a 1% increase in parts cost due to added jumpers and extra ROM space required in the electronics for signature analysis, but total factory costs dropped, because of a 5% decrease in other materials costs. For example, it was no longer necessary to divide the product into small, replaceable modules. Also, BIST reduced service-module inventory at the factory, and decreased administrative and handling costs for failing units returned to the factory.

## 15.1 The Economic Case for BIST

These are some chip-level testability problems of the late 1990s [532]:

- 1. There is an extremely high and still increasing logic-to-pin ratio on the chip. This increasingly makes it harder to accurately observe signals on the device, which is essential for testing.

- 2. VLSI devices are increasingly dense and faster with sub-micron feature sizes.

- 3. There are increasingly long test-pattern generation and test application times.

- 4. Prohibitive amounts of test data must be stored in the automatic test equipment (ATE.)

- 5. There is increasing difficulty in performing at-speed (rated clock) testing using external ATE. For clock rates approaching 1 GHz, at-speed testing with an ATE is very expensive due to pin inductance and high tester pin costs.

- 6. Designers are unfamiliar with the gate-level structure of their designs, since logic is now automatically synthesized from the VHDL or Verilog hardware description languages. This compounds the problem of testability insertion.

- 7. There is a lack of skilled test engineers.

Complexity. One unfortunate property of large VLSI circuits is that testing cannot be easily partitioned. Consider two cascaded devices. There is frequently no simple way to obtain tests for the complete system from tests for the individual parts. In fact, even though each part is fully testable and has a test set that gives 100% stuckfault coverage, the cascaded connection of the two parts will often have untestable and redundant hardware and much lower stuck-fault coverage. In other words, testing is a global problem. It is well known that there is no simple way to create tests for an entire printed circuit board (PCB) from tests for the chips on the board. For

design and test development effort, BIST provides a way to hierarchically decompose the electronic system-under-test, so this allows sub-assemblies to be first run through a BIST cycle, and if there are no faults, then boards in the system are run through a BIST cycle. Finally, if there are no board faults, then the entire system can be run through a BIST cycle. As an example, consider a system containing boards, which in turn contain chips. For a chip test, the system sends a control signal to the PCB, which then activates self-test on the desired chip, and sends the test result back to the system. BIST efficiently tests embedded components and interconnect, thus reducing the burden on system-level test, which now only needs to verify the synergy among the functional components [36]. When faults occur, the BIST hardware should be designed to indicate via an error signal or bus which sub-assembly is faulty. This greatly reduces repair costs.

**Quality.** Typical quality requirements are 98% single stuck-fault coverage or 100% interconnect fault coverage. The reject ratio is the percentage of faulty parts in the number of parts passing a test. The goal of testing at many companies is a low reject ratio, e.g., 1 in 10,000, at reasonable cost. The Motorola six sigma project has a goal of lowering this number to 1 in 100,000 [532]. In huge systems, this is attainable only through design for testability (DFT), and BIST is the preferred form of DFT.

**Test Generation Problems.** It is difficult to carry a test stimulus involving hundreds of chip inputs through many layers of circuitry to the chip-under-test, and then convey the test result back through the many circuit layers to an observable point. BIST localizes testing, which eliminates these problems.

**Test Application Problems.** In the past, in-circuit testing (ICT) [69] used a bedof-nails fixture customized for the PCB-under-test. The bed-of-nails tester applied stimuli to the solder balls on the back of the PCB where the component leads were soldered to the PCB. Power was applied only to the component under test – all others in the PCB were left unpowered. It was effective for chip diagnosis and board wiring tests. However, ICT is not effective unless the PCB is removed from the system, so it is not helpful in system-level diagnosis. Also, surface-mount technology (SMT) components are often mounted densely on both sides of the board, and the PCB wire pitch is also too small for accurate probing of the back of the board by the bedof-nails tester. Therefore, ICT is no longer a solution. BIST, however, solves these problems by eliminating expensive ATE, and BIST also lets us use the same tests and test circuits that are used at the system level [36, 37]. With BIST, there can be virtually unlimited circuit access via test points designed into the circuit through scan chains, resulting in an electronic bed-of-nails [33]. Another advantage of BIST is that the testing capability grows with the VLSI technology, whereas with external testing, the test capability always lags behind the VLSI technology capability. Logic gates and transistors are relatively cheap compared to the labor needed to develop test programs, the cost of automatic test equipment, and the cost of real time for the tests to be run on production chips with ATE [33].

An additional benefit of BIST is lower test development cost, because BIST can be automatically added to a circuit with a CAD tool. Also, BIST generally provides a 90 to 95% fault coverage, and even 99% in exceptional cases [33]. The test engineer need no longer worry about backdriving problems of in-circuit test (where electrical stimuli provided to the middle of the circuitry damage outputs of logic gates), or how much memory is available in the ATE.

| Table 19.1. Built-in self-testing costs. |        |        |                       |            |           |              |  |

|------------------------------------------|--------|--------|-----------------------|------------|-----------|--------------|--|

| Level                                    | Design | Fabri- | Prod.                 | Mainte-    | Diagnosis | Service      |  |

|                                          | & test | cation | $\operatorname{test}$ | nance test | & repair  | interruption |  |

| CHIPS                                    | +/-    | +      | =                     |            |           |              |  |

| BOARDS                                   | +/-    | +      | 1                     |            |           |              |  |

| SYSTEMS                                  | +/-    | +      | =                     | _          | =         | =            |  |

Table 15.1: Built-in self-testing costs.

Table 15.1 [36, 37] shows the relative BIST costs at the chip, board, and system levels of packaging. BIST always requires added circuit hardware for a test controller to operate the testing process, design for testability hardware in the circuit to improve fault coverages during BIST, a hardware pattern generator to generate test-patterns algorithmically during testing, and some form of hardware response compacter to compact the circuit response during testing. We see an increase in fabrication costs at all three levels of circuit packaging. The BIST cost is frequently measured in terms of the added chip/board area required for the BIST hardware. The relative costs of added logic gates are declining, because hardware continues to become cheaper, but the relative costs of added long wires for test mode control are not really decreasing. This cost can also include added circuit delay, due to the extra device loads and delays from the test hardware. This may require a slight increase in the clock rate, and additional electrical adjustments to the design. Also, the test hardware can consume extra power, which is an additional cost. Since the BIST circuitry uses chip area, a final BIST cost is a decrease in the chip yield and chip reliability, due to the increased chip area [33]. BIST feasibility for a system must be evaluated using benefit-cost analysis, in the context of assessing total life cycle costs. Table 15.2 [33] gives more detailed metrics for evaluating BIST costs.

## 15.1.1 Chip/Board Area Cost vs. Tester Cost

At all three levels, BIST reduces testing costs. In order to understand why, consider the example of a 1 GHz microprocessor on a chip with 800 pins. For reliable stuck-fault and limited transition-delay fault testing, we should conduct the test at the rated clock speed. This forces us to use the Advantest Model T6682 1 GHz ATE, which can sample circuit outputs at this rate. The tester costs 800  $pins \times$

<sup>+</sup> cost increase; - cost reduction; +/- cost increase  $\approx$  cost saving (neutral or slight saving)

Table 15.2: Metrics for evaluating BIST.

| characteristics  Single stuck-at faults in functional circuitry  Sequential faults in functional circuitry  Delay faults  Single stuck-at faults in BIST circuitry  Fault Coverage —  % of faults detected in functional circuitry  % of faults detected in the BIST circuitry  Associated  Area overhead — Additional active area and interconnect  Pin overhead — Additional pins. At least 1 pin is required to control whether BIST operates or not. One can design circuits that put the chip into BIST mode without using an extra pin, by applying a voltage level not normally used (e.g., 12 V instead of 0 or 5 V) to a pin. Additional input (output) pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 | Table 19.2. Metrics for evaluating D151.                          |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------|--|--|--|--|--|--|

| Sequential faults in functional circuitry Delay faults Single stuck-at faults in BIST circuitry Fault Coverage — % of faults detected in functional circuitry % of faults detected in the BIST circuitry Associated Costs Area overhead — Additional active area and interconnect Pin overhead — Additional pins. At least 1 pin is required to control whether BIST operates or not. One can design circuits that put the chip into BIST mode without using an extra pin, by applying a voltage level not normally used (e.g., 12 V instead of 0 or 5 V) to a pin. Additional input (output) pins for BIST are obtained by pin multiplexing, where input (output) pins are multiplexed into the BIST circuit when in BIST mode. The MUX adds a slight performance penalty. Performance overhead — added path delays due to BIST Yield loss — due to increased area or more chips in the system Reliability reduction — due to increased area Increased design effort and time Testability of the BIST hardware. The BIST hardware complexity increases when the BIST hardware is made testable. Associated benefits Reduced cost of testing and maintenance Lower test generation cost Reduced storage and maintenance of test patterns Simpler and less costly ATE Ability to test many units cost-effectively in parallel Shorter test application times Ability to test at system speed Other Degree to which BIST structure is function independent Diagnostic resolution | Fault           |                                                                   |  |  |  |  |  |  |

| Delay faults Single stuck-at faults in BIST circuitry Fault Coverage — % of faults detected in functional circuitry % of faults detected in the BIST circuitry Associated costs Pin overhead — Additional active area and interconnect Pin overhead — Additional pins. At least 1 pin is required to control whether BIST operates or not. One can design circuits that put the chip into BIST mode without using an extra pin, by applying a voltage level not normally used (e.g., 12 V instead of 0 or 5 V) to a pin. Additional input (output) pins for BIST are obtained by pin multiplexing, where input (output) pins are multiplexed into the BIST circuit when in BIST mode. The MUX adds a slight performance penalty. Performance overhead — added path delays due to BIST Yield loss — due to increased area or more chips in the system Reliability reduction — due to increased area Increased design effort and time Testability of the BIST hardware. The BIST hardware complexity increases when the BIST hardware is made testable.  Associated benefits  Associated benefits  Reduced cost of testing and maintenance Lower test generation cost Reduced storage and maintenance of test patterns Simpler and less costly ATE Ability to test many units cost-effectively in parallel Shorter test application times Ability to test at system speed  Other Degree to which BIST structure is function independent Diagnostic resolution                    | characteristics | Single stuck-at faults in functional circuitry                    |  |  |  |  |  |  |

| Single stuck-at faults in BIST circuitry Fault Coverage — % of faults detected in functional circuitry % of faults detected in the BIST circuitry Associated costs Area overhead — Additional active area and interconnect Pin overhead — Additional pins. At least 1 pin is required to control whether BIST operates or not. One can design circuits that put the chip into BIST mode without using an extra pin, by applying a voltage level not normally used (e.g., 12 V instead of 0 or 5 V) to a pin. Additional input (output) pins for BIST are obtained by pin multiplexing, where input (output) pins are multiplexed into the BIST circuit when in BIST mode. The MUX adds a slight performance penalty. Performance overhead — added path delays due to BIST Yield loss — due to increased area or more chips in the system Reliability reduction — due to increased area Increased design effort and time Testability of the BIST hardware. The BIST hardware complexity increases when the BIST hardware is made testable.  Associated benefits Reduced cost of testing and maintenance Lower test generation cost Reduced storage and maintenance of test patterns Simpler and less costly ATE Ability to test many units cost-effectively in parallel Shorter test application times Ability to test at system speed  Other Degree to which BIST structure is function independent Diagnostic resolution                                                      |                 | Sequential faults in functional circuitry                         |  |  |  |  |  |  |

| Fault Coverage — % of faults detected in functional circuitry % of faults detected in the BIST circuitry  Associated costs  Area overhead — Additional active area and interconnect Pin overhead — Additional pins. At least 1 pin is required to control whether BIST operates or not. One can design circuits that put the chip into BIST mode without using an extra pin, by applying a voltage level not normally used (e.g., 12 V instead of 0 or 5 V) to a pin. Additional input (output) pins for BIST are obtained by pin multiplexing, where input (output) pins are multiplexed into the BIST circuit when in BIST mode. The MUX adds a slight performance penalty. Performance overhead — added path delays due to BIST Yield loss — due to increased area or more chips in the system Reliability reduction — due to increased area Increased design effort and time Testability of the BIST hardware. The BIST hardware complexity increases when the BIST hardware is made testable.  Associated Beduced cost of testing and maintenance Lower test generation cost Reduced storage and maintenance of test patterns Simpler and less costly ATE Ability to test many units cost-effectively in parallel Shorter test application times Ability to test at system speed  Other Degree to which BIST structure is function independent Diagnostic resolution                                                                                                      |                 | Delay faults                                                      |  |  |  |  |  |  |

| % of faults detected in functional circuitry % of faults detected in the BIST circuitry  Associated costs  Area overhead – Additional active area and interconnect Pin overhead – Additional pins. At least 1 pin is required to control whether BIST operates or not. One can design circuits that put the chip into BIST mode without using an extra pin, by applying a voltage level not normally used (e.g., 12 V instead of 0 or 5 V) to a pin. Additional input (output) pins for BIST are obtained by pin multiplexing, where input (output) pins are multiplexed into the BIST circuit when in BIST mode. The MUX adds a slight performance penalty. Performance overhead – added path delays due to BIST Yield loss – due to increased area or more chips in the system Reliability reduction – due to increased area Increased design effort and time Testability of the BIST hardware. The BIST hardware complexity increases when the BIST hardware is made testable.  Associated Benefits  Associated Beduced cost of testing and maintenance Lower test generation cost Reduced storage and maintenance of test patterns Simpler and less costly ATE Ability to test many units cost-effectively in parallel Shorter test application times Ability to test at system speed  Other  Degree to which BIST structure is function independent Diagnostic resolution                                                                                                 |                 |                                                                   |  |  |  |  |  |  |

| Associated costs  Area overhead – Additional active area and interconnect Pin overhead – Additional pins. At least 1 pin is required to control whether BIST operates or not. One can design circuits that put the chip into BIST mode without using an extra pin, by applying a voltage level not normally used (e.g., 12 V instead of 0 or 5 V) to a pin. Additional input (output) pins for BIST are obtained by pin multiplexing, where input (output) pins are multiplexed into the BIST circuit when in BIST mode. The MUX adds a slight performance penalty. Performance overhead – added path delays due to BIST Yield loss – due to increased area or more chips in the system Reliability reduction – due to increased area Increased design effort and time Testability of the BIST hardware. The BIST hardware complexity increases when the BIST hardware is made testable.  Associated benefits  Reduced cost of testing and maintenance Lower test generation cost Reduced storage and maintenance of test patterns Simpler and less costly ATE Ability to test many units cost-effectively in parallel Shorter test application times Ability to test at system speed  Other Characteristics Diagnostic resolution                                                                                                                                                                                                                                             |                 |                                                                   |  |  |  |  |  |  |

| Associated costs  Area overhead – Additional active area and interconnect Pin overhead – Additional pins. At least 1 pin is required to control whether BIST operates or not. One can design circuits that put the chip into BIST mode without using an extra pin, by applying a voltage level not normally used (e.g., 12 V instead of 0 or 5 V) to a pin. Additional input (output) pins for BIST are obtained by pin multiplexing, where input (output) pins are multiplexed into the BIST circuit when in BIST mode. The MUX adds a slight performance penalty. Performance overhead – added path delays due to BIST Yield loss – due to increased area or more chips in the system Reliability reduction – due to increased area Increased design effort and time  Testability of the BIST hardware. The BIST hardware complexity increases when the BIST hardware is made testable.  Associated Reduced cost of testing and maintenance benefits Lower test generation cost Reduced storage and maintenance of test patterns Simpler and less costly ATE Ability to test many units cost-effectively in parallel Shorter test application times Ability to test at system speed  Other Degree to which BIST structure is function independent Diagnostic resolution                                                                                                                                                                                                      |                 |                                                                   |  |  |  |  |  |  |

| Pin overhead – Additional pins. At least 1 pin is required to control whether BIST operates or not. One can design circuits that put the chip into BIST mode without using an extra pin, by applying a voltage level not normally used (e.g., 12 V instead of 0 or 5 V) to a pin. Additional input (output) pins for BIST are obtained by pin multiplexing, where input (output) pins are multiplexed into the BIST circuit when in BIST mode. The MUX adds a slight performance penalty. Performance overhead – added path delays due to BIST Yield loss – due to increased area or more chips in the system Reliability reduction – due to increased area Increased design effort and time Testability of the BIST hardware. The BIST hardware complexity increases when the BIST hardware is made testable. Associated Beduced cost of testing and maintenance Lower test generation cost Reduced storage and maintenance of test patterns Simpler and less costly ATE Ability to test many units cost-effectively in parallel Shorter test application times Ability to test at system speed  Other  Other  Degree to which BIST structure is function independent Diagnostic resolution                                                                                                                                                                                                                                                                                   |                 | % of faults detected in the BIST circuitry                        |  |  |  |  |  |  |

| control whether BIST operates or not. One can design circuits that put the chip into BIST mode without using an extra pin, by applying a voltage level not normally used (e.g., 12 V instead of 0 or 5 V) to a pin. Additional input (output) pins for BIST are obtained by pin multiplexing, where input (output) pins are multiplexed into the BIST circuit when in BIST mode. The MUX adds a slight performance penalty. Performance overhead – added path delays due to BIST Yield loss – due to increased area or more chips in the system Reliability reduction – due to increased area Increased design effort and time  Testability of the BIST hardware. The BIST hardware complexity increases when the BIST hardware is made testable.  Associated benefits Reduced cost of testing and maintenance Lower test generation cost Reduced storage and maintenance of test patterns Simpler and less costly ATE Ability to test many units cost-effectively in parallel Shorter test application times Ability to test at system speed  Other Degree to which BIST structure is function independent Characteristics Diagnostic resolution                                                                                                                                                                                                                                                                                                                              | Associated      | Area overhead – Additional active area and interconnect           |  |  |  |  |  |  |

| that put the chip into BIST mode without using an extra pin, by applying a voltage level not normally used (e.g., 12 V instead of 0 or 5 V) to a pin. Additional input (output) pins for BIST are obtained by pin multiplexing, where input (output) pins are multiplexed into the BIST circuit when in BIST mode. The MUX adds a slight performance penalty. Performance overhead – added path delays due to BIST Yield loss – due to increased area or more chips in the system Reliability reduction – due to increased area Increased design effort and time Testability of the BIST hardware. The BIST hardware complexity increases when the BIST hardware is made testable.  Associated Reduced cost of testing and maintenance Lower test generation cost Reduced storage and maintenance of test patterns Simpler and less costly ATE Ability to test many units cost-effectively in parallel Shorter test application times Ability to test at system speed  Other Degree to which BIST structure is function independent Diagnostic resolution                                                                                                                                                                                                                                                                                                                                                                                                                      | costs           | Pin overhead – Additional pins. At least 1 pin is required to     |  |  |  |  |  |  |

| pin, by applying a voltage level not normally used (e.g., 12 V instead of 0 or 5 V) to a pin. Additional input (output) pins for BIST are obtained by pin multiplexing, where input (output) pins are multiplexed into the BIST circuit when in BIST mode. The MUX adds a slight performance penalty. Performance overhead – added path delays due to BIST Yield loss – due to increased area or more chips in the system Reliability reduction – due to increased area Increased design effort and time Testability of the BIST hardware. The BIST hardware complexity increases when the BIST hardware is made testable.  Associated Reduced cost of testing and maintenance benefits Lower test generation cost Reduced storage and maintenance of test patterns Simpler and less costly ATE Ability to test many units cost-effectively in parallel Shorter test application times Ability to test at system speed  Other Degree to which BIST structure is function independent Diagnostic resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 | control whether BIST operates or not. One can design circuits     |  |  |  |  |  |  |

| instead of 0 or 5 V) to a pin. Additional input (output) pins for BIST are obtained by pin multiplexing, where input (output) pins are multiplexed into the BIST circuit when in BIST mode. The MUX adds a slight performance penalty. Performance overhead – added path delays due to BIST Yield loss – due to increased area or more chips in the system Reliability reduction – due to increased area Increased design effort and time Testability of the BIST hardware. The BIST hardware complexity increases when the BIST hardware is made testable.  Associated Benefits Reduced cost of testing and maintenance benefits Lower test generation cost Reduced storage and maintenance of test patterns Simpler and less costly ATE Ability to test many units cost-effectively in parallel Shorter test application times Ability to test at system speed  Other Characteristics Diagnostic resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 | that put the chip into BIST mode without using an extra           |  |  |  |  |  |  |

| for BIST are obtained by pin multiplexing, where input (output) pins are multiplexed into the BIST circuit when in BIST mode. The MUX adds a slight performance penalty. Performance overhead – added path delays due to BIST Yield loss – due to increased area or more chips in the system Reliability reduction – due to increased area Increased design effort and time Testability of the BIST hardware. The BIST hardware complexity increases when the BIST hardware is made testable.  Associated Reduced cost of testing and maintenance benefits Lower test generation cost Reduced storage and maintenance of test patterns Simpler and less costly ATE Ability to test many units cost-effectively in parallel Shorter test application times Ability to test at system speed  Other Degree to which BIST structure is function independent Diagnostic resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 | pin, by applying a voltage level not normally used (e.g., $12\ V$ |  |  |  |  |  |  |

| pins are multiplexed into the BIST circuit when in BIST mode. The MUX adds a slight performance penalty. Performance overhead – added path delays due to BIST Yield loss – due to increased area or more chips in the system Reliability reduction – due to increased area Increased design effort and time Testability of the BIST hardware. The BIST hardware complexity increases when the BIST hardware is made testable.  Associated Beduced cost of testing and maintenance Lower test generation cost Reduced storage and maintenance of test patterns Simpler and less costly ATE Ability to test many units cost-effectively in parallel Shorter test application times Ability to test at system speed  Other Characteristics Diagnostic resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 |                                                                   |  |  |  |  |  |  |

| in BIST mode. The MUX adds a slight performance penalty.  Performance overhead – added path delays due to BIST Yield loss – due to increased area or more chips in the system Reliability reduction – due to increased area Increased design effort and time Testability of the BIST hardware. The BIST hardware complexity increases when the BIST hardware is made testable.  Associated benefits Reduced cost of testing and maintenance Lower test generation cost Reduced storage and maintenance of test patterns Simpler and less costly ATE Ability to test many units cost-effectively in parallel Shorter test application times Ability to test at system speed  Other Characteristics Diagnostic resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 | for BIST are obtained by pin multiplexing, where input (output)   |  |  |  |  |  |  |

| Performance overhead – added path delays due to BIST Yield loss – due to increased area or more chips in the system Reliability reduction – due to increased area Increased design effort and time Testability of the BIST hardware. The BIST hardware complexity increases when the BIST hardware is made testable.  Associated Reduced cost of testing and maintenance Lower test generation cost Reduced storage and maintenance of test patterns Simpler and less costly ATE Ability to test many units cost-effectively in parallel Shorter test application times Ability to test at system speed  Other Characteristics Diagnostic resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |                                                                   |  |  |  |  |  |  |

| Yield loss – due to increased area or more chips in the system Reliability reduction – due to increased area Increased design effort and time Testability of the BIST hardware. The BIST hardware complexity increases when the BIST hardware is made testable.  Associated Reduced cost of testing and maintenance Lower test generation cost Reduced storage and maintenance of test patterns Simpler and less costly ATE Ability to test many units cost-effectively in parallel Shorter test application times Ability to test at system speed  Other Characteristics Diagnostic resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 | -                                                                 |  |  |  |  |  |  |

| Reliability reduction – due to increased area Increased design effort and time Testability of the BIST hardware. The BIST hardware complexity increases when the BIST hardware is made testable.  Associated Beduced cost of testing and maintenance Lower test generation cost Reduced storage and maintenance of test patterns Simpler and less costly ATE Ability to test many units cost-effectively in parallel Shorter test application times Ability to test at system speed  Other Characteristics Diagnostic resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 | Performance overhead – added path delays due to BIST              |  |  |  |  |  |  |

| Increased design effort and time Testability of the BIST hardware. The BIST hardware complexity increases when the BIST hardware is made testable.  Associated Benefits Reduced cost of testing and maintenance Lower test generation cost Reduced storage and maintenance of test patterns Simpler and less costly ATE Ability to test many units cost-effectively in parallel Shorter test application times Ability to test at system speed  Other Characteristics Diagnostic resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |                                                                   |  |  |  |  |  |  |

| Testability of the BIST hardware. The BIST hardware complexity increases when the BIST hardware is made testable.  Associated Reduced cost of testing and maintenance Lower test generation cost Reduced storage and maintenance of test patterns Simpler and less costly ATE Ability to test many units cost-effectively in parallel Shorter test application times Ability to test at system speed  Other Degree to which BIST structure is function independent Diagnostic resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 | Reliability reduction – due to increased area                     |  |  |  |  |  |  |

| Associated Reduced cost of testing and maintenance benefits Lower test generation cost Reduced storage and maintenance of test patterns Simpler and less costly ATE Ability to test many units cost-effectively in parallel Shorter test application times Ability to test at system speed  Other Characteristics Diagnostic resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 | Increased design effort and time                                  |  |  |  |  |  |  |

| Associated Beduced cost of testing and maintenance Lower test generation cost Reduced storage and maintenance of test patterns Simpler and less costly ATE Ability to test many units cost-effectively in parallel Shorter test application times Ability to test at system speed Other Degree to which BIST structure is function independent Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 | Testability of the BIST hardware. The BIST hardware               |  |  |  |  |  |  |

| benefits  Lower test generation cost  Reduced storage and maintenance of test patterns  Simpler and less costly ATE  Ability to test many units cost-effectively in parallel  Shorter test application times  Ability to test at system speed  Other  Characteristics  Diagnostic resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 | complexity increases when the BIST hardware is made testable.     |  |  |  |  |  |  |

| Reduced storage and maintenance of test patterns Simpler and less costly ATE Ability to test many units cost-effectively in parallel Shorter test application times Ability to test at system speed  Other Characteristics Diagnostic resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Associated      | Reduced cost of testing and maintenance                           |  |  |  |  |  |  |

| Simpler and less costly ATE Ability to test many units cost-effectively in parallel Shorter test application times Ability to test at system speed Other Characteristics Diagnostic resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | benefits        | Lower test generation cost                                        |  |  |  |  |  |  |

| Ability to test many units cost-effectively in parallel Shorter test application times Ability to test at system speed Other Characteristics Diagnostic resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 | Reduced storage and maintenance of test patterns                  |  |  |  |  |  |  |

| Shorter test application times Ability to test at system speed Other Degree to which BIST structure is function independent characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 | Simpler and less costly ATE                                       |  |  |  |  |  |  |

| Ability to test at system speed  Other Degree to which BIST structure is function independent characteristics Diagnostic resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 | Ability to test many units cost-effectively in parallel           |  |  |  |  |  |  |

| Other Degree to which BIST structure is function independent characteristics Diagnostic resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 | Shorter test application times                                    |  |  |  |  |  |  |

| characteristics Diagnostic resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 | · · · · · · · · · · · · · · · · · · ·                             |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 | _                                                                 |  |  |  |  |  |  |

| Effect of engineering changes on BIST structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | characteristics |                                                                   |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 | Effect of engineering changes on BIST structure                   |  |  |  |  |  |  |

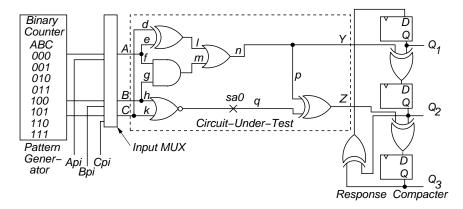

\$6,000 per pin = \$ 4,800,000, but there is no chip area cost due to testing, because we do not use on-chip BIST hardware. Therefore, there is a huge initial capital cost for the ATE, but there is no recurring chip area cost on each chip for test hardware. If, instead, we provide BIST hardware, then the need for a very high-speed ATE is eliminated, except to test the wires from the circuit pins to the  $Input\ MUX$ , and from the circuit outputs to the output pins. The number of tests for that is very short, say perhaps 7 or 8 patterns and measurements per pin, and the cost of this can be safely ignored in this analysis. Therefore, with BIST doing all stuck-fault and transition-delay fault testing, we need a  $1\ GHz$  signal oscillator to clock the chip, and we need the ATE only to provide DC command signals to tell the microprocessor to perform BIST. Finally, we need an ATE to read out the success or failure DC signal for BIST from a circuit pin. In this case, we can use an inexpensive,  $20\ MHz$  ATE that costs roughly \$391 per pin, so our cost is  $800\ pins \times \$391\ per\ pin = \$312,800$ , a savings of \$4,487,200. This example is hardly far fetched. On-chip clock rates are expected to rise above  $1\ GHz$ , and at present, no ATE exists to test a circuit above  $1\ GHz$ .

For design and test development, BIST significantly reduces the costs of automatic test-pattern generation (ATPG), and reduces the likelihood of disastrous product introduction delays because a fully-designed system cannot be tested. Such a delay has occurred in the Intel Merced<sup>TM</sup> project due to unexpected delays in inserting testability hardware into the chip, and fabrication line problems. There is a slight cost increase due to BIST in design and test development, because of the added time required to design and add pattern generators, response compacters, and testability hardware. However, our experience is that this is less costly than test development with ATPG.

## 15.1.2 Chip/Board Area Cost vs. System Downtime Cost

The true economic benefits of BIST show up in the last three columns of Table 15.1. Without BIST, maintenance test requires the presence of an expensive ATE at the site of the failing system, and this is a significant cost. With BIST. there is no need for an ATE, so this reduces system test cost. For boards and systems, BIST drastically reduces the diagnosis and repair cost, by quickly determining and indicating which sub-assembly or component is faulty, without the extensive labor and equipment normally required. This great reduction in diagnosis and repair time naturally leads to a major shortening in service interruption, particularly at the system level. An example of an application where service interruptions must be minimal is the # 5 ESS telephone exchange designed by Lucent Technologies. The exchange is designed to have, at most, a fraction of a second down time per year, because the lost revenue to an operating phone company when long distance calls cannot be made is quite severe. Another example is the credit card operations of American Express, which must be completed in a timely way so that the company knows which of its customers should be allowed additional credit and which should not. A final example is the Quotron system of the New York Stock Exchange for electronic trading of stocks. Down time of this system can cost billions of dollars per hour in lost trading opportunities. When viewed in this light, the added costs

of BIST hardware may be very minor compared with the severe cost of service interruption. A further benefit of BIST is its cost reduction for diagnosis and repair. Whenever any consumer home appliance breaks, the minimal cost just to have a repairman come out and look at the appliance is usually \$100, and the total repair cost may exceed \$175. It may be possible to justify BIST on a benefit-cost basis in personal computers and other home electronic appliances costing more than \$1,500.

The reader may recall the rule of ten in testing costs from Chapter 3. If it costs \$0.50 to detect a fault at the chip level, it will cost \$5 to detect the same fault at the board level, \$50 at the system test level, and \$500 for a field repair for the same fault (because of the expense of sending out a serviceman to a customer site.) Therefore, test cost reductions due to BIST in Table 15.1 in the board and system columns are particularly important. It is most economical to detect problems early.

## 15.2 Random Logic BIST

#### 15.2.1 Definitions

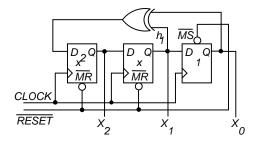

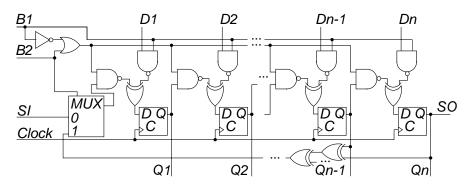

- BILBO Built-In Logic Block Observer. This is a bank of circuit flip-flops with added testing hardware, which can be configured to make the flip-flops behave like a scan chain, a linear feedback shift register (LFSR) pattern generator, an LFSR-based response compacter, or merely as D flip-flops.

- Concurrent Testing A testing process that detects faults during normal system operation.

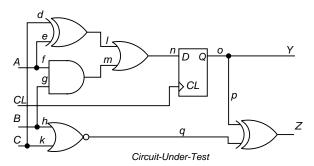

- CUT Circuit-Under-Test

- Exhaustive Testing A BIST approach in which all  $2^n$  possible patterns are applied to n circuit inputs.

- Irreducible Polynomial A Boolean polynomial that cannot be factored.

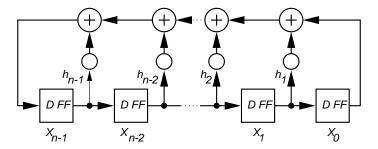

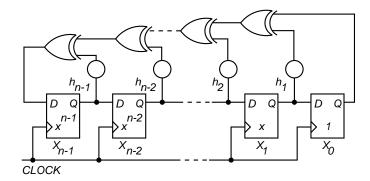

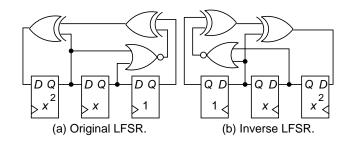

- LFSR *Linear Feedback Shift Register*. This is hardware that generates an exhaustive or pseudo-random pattern sequence of test patterns, and can also be used as a response compacter.

- Non-Concurrent Testing A testing process that requires suspension of normal system operation to test for faults.

- Primitive Polynomial A primitive Boolean polynomial p(x) has the property that we can compute increasing powers of x modulo p(x), and obtain all possible non-zero polynomials of degree less than p(x). We compute the remainders of x/p(x),  $x^2/p(x)$ , and so on. A primitive polynomial defines a mathematical number system that has the properties of a mathematical field.

- Pseudo-Exhaustive Testing A BIST approach in which a circuit having n primary inputs (PIs) is broken into smaller, overlapping blocks, each with < n inputs. Each of the smaller blocks is tested exhaustively.

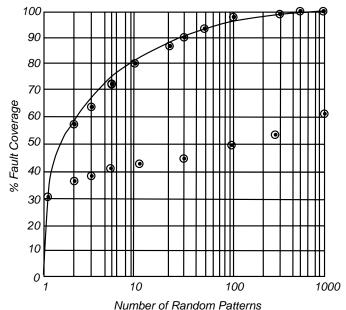

- Pseudo-Random Testing A BIST pattern generator that produces, via an algorithm, a subset of all possible tests that has most of the properties of randomly-generated tests. The random patterns must have a statistically high enough fault coverage to ensure a good test.

- TPG Hardware Test-Pattern Generator

#### 15.2.2 BIST Process

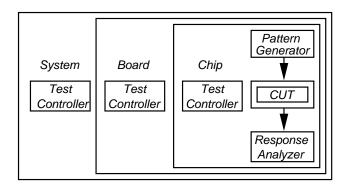

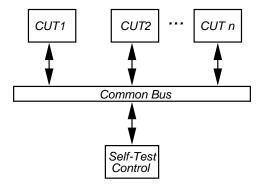

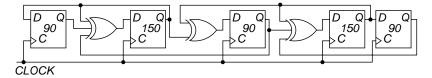

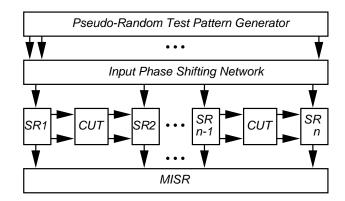

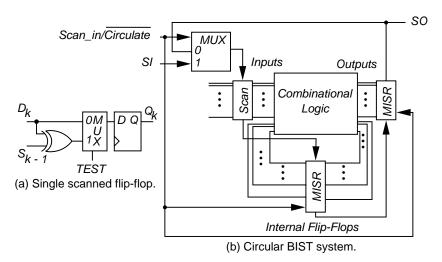

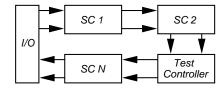

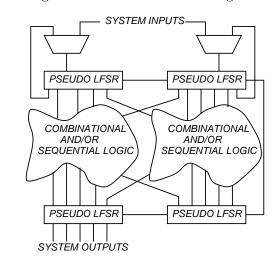

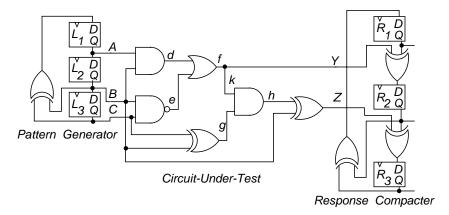

Figure 15.1: BIST hierarchy.

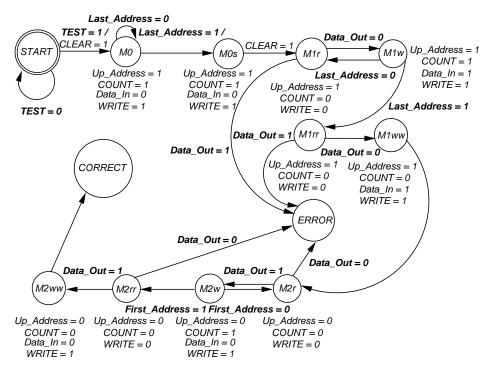

Figure 15.1 shows the BIST system hierarchy and all three levels of packaging mentioned earlier. The system has several PCBs, each of which, in turn, has multiple chips. The system *Test Controller* can activate self-test simultaneously on all PCBs. Each Test Controller on each PCB can activate self-test on all chips on the PCB. The Test Controller on a chip executes self-test for that chip, and then transmits the result to the PCB Test Controller, which accumulates test results from all chips on the board and sends the results to the system Test Controller. The system Test Controller uses all of these results to isolate faulty chips and boards [36, 37].

System diagnosis is effective only if the self-test procedures are thorough. For BIST, fault coverage is a major issue. Other issues are chip area overhead, its impact on chip yield, the cost of the additional chip pins required for test, the performance penalty in terms of added circuit delay, and extra power requirements. For BIST, the test engineer frequently, but not always, modifies the chip logic to make all latches and flip-flops controllable, perhaps by using the scan technique [36, 37].

#### **BIST Implementations**

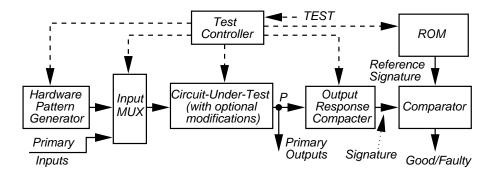

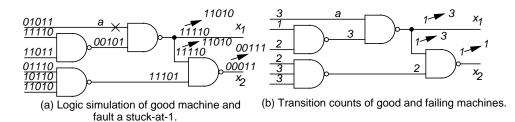

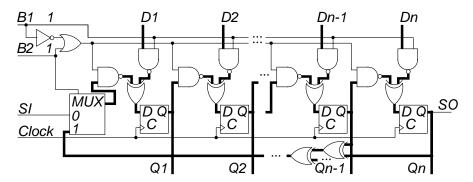

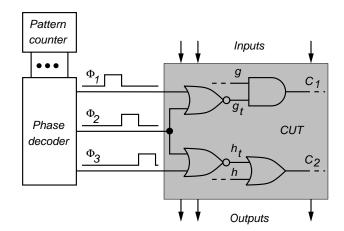

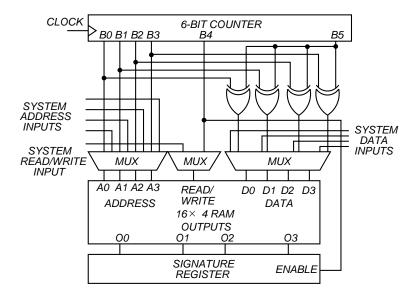

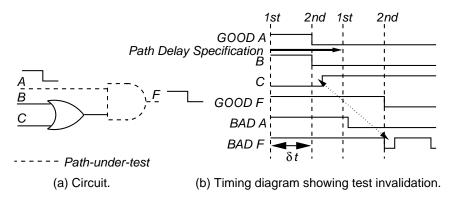

Figure 15.2 shows typical BIST hardware in more detail. Note that the wires from PIs to the  $Input\ MUX$  and the wires from circuit outputs P to  $primary\ outputs$  (POs) cannot be tested by BIST. These wires, instead, require another testing method, such as an external ATE or JTAG Boundary Scan hardware. Figure 15.2 also shows how a comparator compares the signature produced by the data compacter with a reference signature stored in a ROM during BIST. This comparator and ROM hardware can frequently be implemented with a single logic gate with 32

Figure 15.2: BIST process.

or fewer inputs. This is acceptable only when the comparison can occur at extremely low rates of circuit operation, since this logic gate is exceedingly slow.

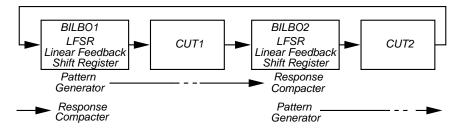

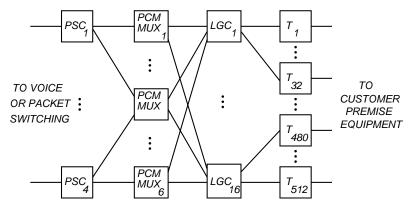

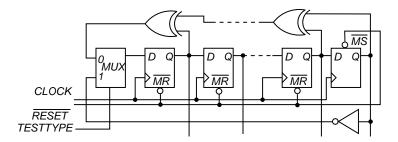

Figure 15.3: Multi-purpose registers in a BIST implementation.

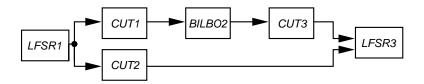

Figure 15.4: Complex BIST implementation.

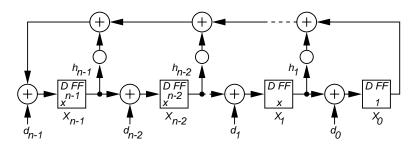

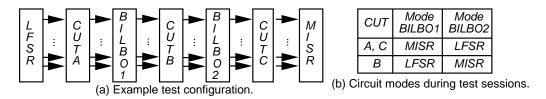

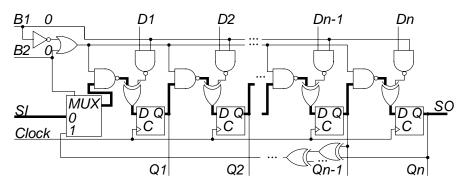

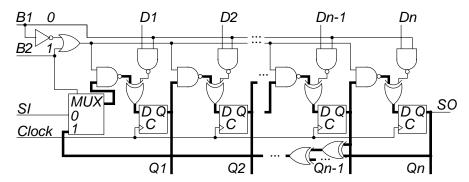

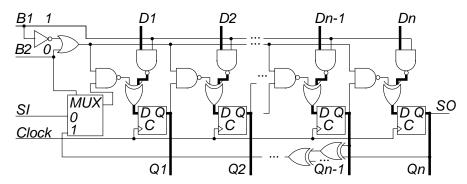

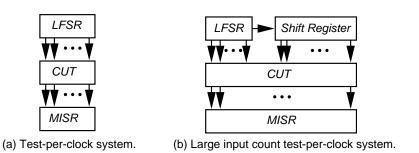

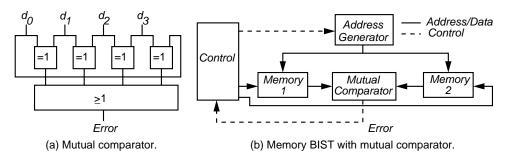

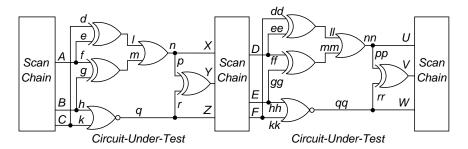

Figure 15.3 shows a BIST implementation using built-in logic block observers (BILBOs) [364]. A BILBO is a bank of D flip-flops in the CUT that has test hardware added to make it behave in one of four modes:

- As ordinary D flip-flops.

- As a linear feedback shift register (LFSR) hardware pattern generator.

- As an LFSR configured to compact a circuit response.

- As a scan chain.

BILBO1 is configured as an LFSR pattern generator to test CUT1 in the circuit, while BILBO2 is configured as a response compacter to compact the responses of CUT1. During this process, the behavior of CUT2 is ignored. BILBO2 is configured as an LFSR pattern generator to test CUT2 in the circuit, while BILBO1 is

configured as a response compacter to compact the responses of CUT2. During this second process, the behavior of CUT1 is ignored. For the normal system function, both BILBO1 and BILBO2 are configured to behave as simple D flip-flops.

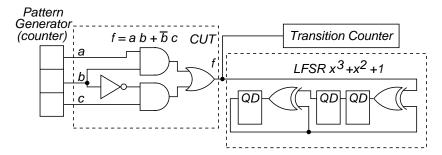

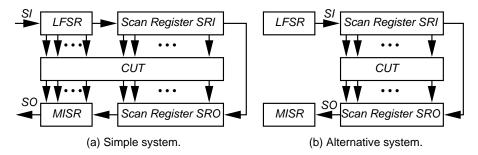

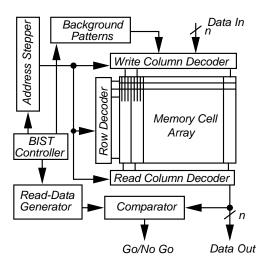

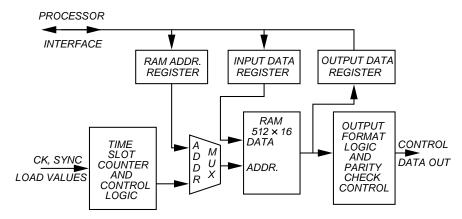

Figure 15.4 shows a more complicated BIST system. Here, *LFSR1* is used to simultaneously generate patterns to test *CUT1* and *CUT2*. *BILBO2* is configured as a response compacter for *CUT1*, while *LFSR3* is configured as a response compacter for *CUT2*. In this mode, inputs to *CUT3* must be held steady so that the outputs of *CUT3* remain stable. In the second test mode, *BILBO2* is configured as a pattern generator for *CUT3*, while *LFSR3* is configured as a response compacter for *CUT3*. The outputs of *CUT1* are ignored, and LFSR1 must be set so that the outputs of *CUT2* are held steady during this second mode. Finally, Figure 15.5 shows a bus-oriented BIST implementation. The *self-test control* broadcasts test-patterns to each of the CUTs over their common bus. The self-test control then awaits bus transactions from each CUT that indicate the CUT's response to the stimulus pattern broadcast over the bus. This allows for a certain amount of concurrency during self-test. In this mechanism, pattern generation for all of the CUTs can happen in parallel, but response compaction is serialized over the bus.

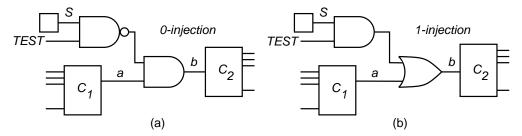

The strategy for overall test control is the most difficult part of BIST design [33]. Care must be taken so that the BIST circuitry, as well as the circuit-under-test, can be tested for stuck-at faults. The BIST circuitry that must operate correctly for BIST to work is referred to as the *hard-core*. Either the hard-core must be minimized, or it must be made testable.

Figure 15.5: Bus-based BIST implementation.

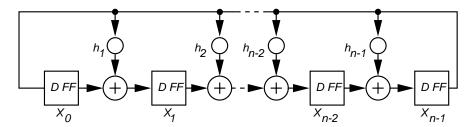

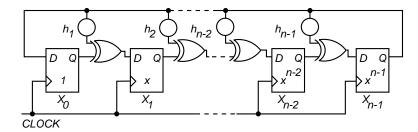

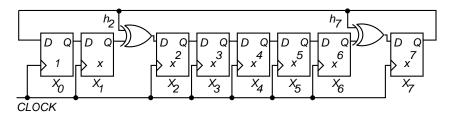

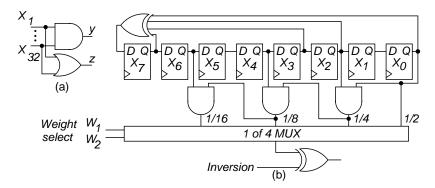

#### 15.2.3 BIST Pattern Generation

The following hardware pattern generation approaches have been used.

- 1. ROM. One method is to store a good test-pattern set (from an ATPG program) in a ROM on the chip, but this is prohibitively expensive in chip area, and will not be discussed further.

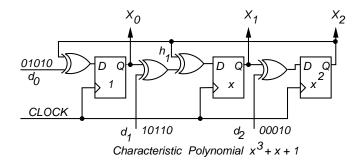

- 2. LFSR. Another method is to use a linear feedback shift register (LFSR) to generate pseudo-random tests. This frequently requires a sequence of 1 million

or more tests to obtain high fault coverages, but the method uses very little hardware and is currently the preferred BIST pattern generation method.

- 3. Binary Counters. A binary counter can generate an exhaustive test sequence, but this can use too much test time if the number of inputs is huge. For example, with 64 inputs and the test-pattern generator clocked at 100 MHz, this takes 51,240,955.8 hours of test time to generate all 2<sup>64</sup> patterns, which is impractical. Therefore, this type of pattern generator must be partitioned. Also, the binary counter requires more hardware than the typical LFSR pattern generator.

- 4. *Modified Counters*. Modified counters have also been successful as test-pattern generators, but they also require long test sequences.

- 5. LFSR and ROM. One of the most effective approaches is to use an LFSR as the primary test mode, and then generate test-patterns with an ATPG program for the faults that are missed by the LFSR sequence. These few additional test-patterns can either be stored in a small ROM on the chip for a second test epoch, they can be embedded in the output of the LFSR, or they can be embedded in a scan chain in order to augment the stuck-fault coverage to 100%.

- 6. Cellular Automaton. In this approach, each pattern generator cell has a few logic gates, a flip-flop, and connections only to neighboring gates. The cell is replicated to produce the cellular automaton.

#### **Exhaustive Pattern Generation**

Exhaustive testing methods are intended to show that:

- 1. Every intended circuit state exists, and

- 2. Every state transition works.

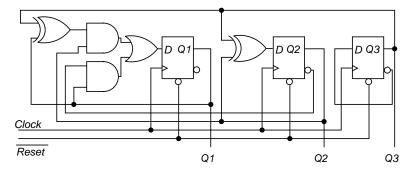

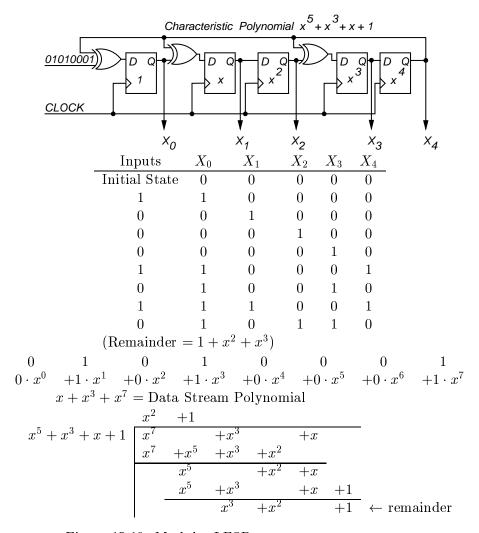

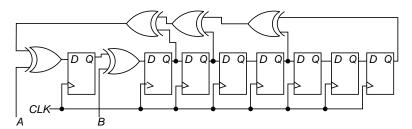

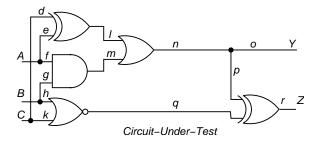

For an n-input circuit, one must test the circuit with all  $2^n$  input vectors, which causes exhaustive testing to be impractical when n > 20. Figure 15.6 shows an exhaustive pattern generator implemented with a binary counter.

**Example 15.1** Exhaustive Test. In the Intel 80386, exhaustive test was used for three control PLAs and for one control ROM using multiple-input signature registers (MISRs) for response compacters.

#### **Pseudo-Exhaustive Pattern Generation**

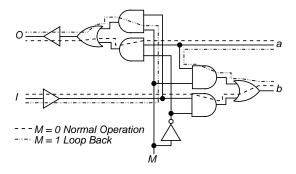

We discuss four methods of pseudo-exhaustive testing:

Figure 15.6: Exhaustive pattern generator.

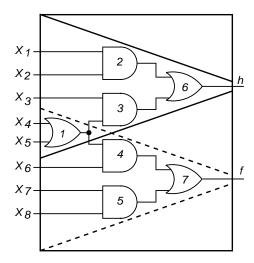

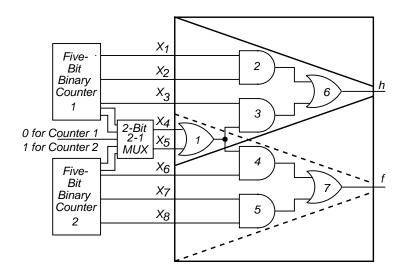

Figure 15.7: Backtracing for pseudo-exhaustive testing.