# High Sensitivity Signatures for Test and Diagnosis of Analog, Mixed-Signal and Radio-Frequency Circuits

by

Suraj Sindia

A dissertation submitted to the Graduate Faculty of

Auburn University

in partial fulfillment of the

requirements for the Degree of

Doctor of Philosophy

Auburn, Alabama August 3, 2013

Keywords: Analog Circuit, Test, Diagnosis, Mixed-Signal Test, Radio-Frequency Test, Signature-Based Test

Copyright 2013 by Suraj Sindia

# Approved by

Vishwani D. Agrawal, Chair, James J. Danaher Professor of Electrical & Computer Eng. Foster F. Dai, Professor of Electrical & Computer Engineering Adit D. Singh, James B. Davis Professor of Electrical & Computer Engineering Alvin Lim, Professor of Computer Science & Software Engineering

#### Abstract

The conventional approach, widely practiced in the industry today, for testing analog circuits is to ensure that the circuit conforms to data-sheet limits on all its specifications. However, such a specification based test methodology suffers from high levels of test cost stemming from long test-times on expensive test equipment. In recent years the situation has only worsened with the advent of mixed signal systems on chip (SoC), to a point where analog circuit test cost is often found to be as much as 50% of the total test cost in spite of analog portions occupying less than 5% of the chip area.

To alleviate the analog circuit test cost problem, a number of techniques exist in the literature that can be broadly classified as (a) fault-model based test or (b) alternate test. Fault model based test techniques direct their tests to identify faults in circuit components much like their digital circuit test counterparts resulting in a test approach that can be easily automated and relies on readily available output measurements on inexpensive test equipment. On the other hand, alternate test techniques test a circuit by building a regression model relating a few easily observable output parameters as signatures of the circuit to the actual circuit specification.

Both these test paradigms for analog circuit test, however, have limited industry acceptance due to a lack of confidence in the defect level and yield loss that the test procedures can guarantee in the face of high manufacturing process variation and low signal levels that are characteristic of modern analog circuits. An important reason for the (typically) high defect level and yield loss resulting from the use of either of these two test paradigms is the unavailability of easily obtainable circuit outputs that are (a) sufficiently sensitive to circuit component values and (b) have a high degree of correlation with circuit specifications.

The main objective of this thesis is to design analog test signatures (and associated test procedures) that are (i) sensitive enough to capture even small variations in circuit components, and (ii) sufficiently correlated to circuit specifications and yet obtainable at limited or no additional hardware and input signal design effort. Additional objectives of this thesis are to: 1) Extend the use of the new signatures to diagnose faulty circuit components in analog circuits. 2) Use the test signatures to distinguish faults resulting from defects caused by manufacturing process related variations. 3) Evaluate the theoretical bounds on the achievable defect level and the resulting yield loss of fault model based test procedures relying on these signatures.

The sensitivity of the proposed test signatures is enhanced by an exponential transformation, called V-Transform. The new test signatures and associated procedures are evaluated using three metrics—test time, defect level (test escapes), and yield loss. We analyze the proposed signatures theoretically in addition to extensive computer simulations and hardware measurements on common RF/analog circuits such as filters and low noise amplifiers. A representative result of one of our experiments is as follows: For 400 low noise amplifier circuits that were tested, we find that the proposed V-transform based signatures resulted in smaller test escape ( $\approx 2\%$ ) and yield loss ( $\approx 3\%$ ) when compared to other prevailing alternate test or fault-model based test methods, while significantly reducing test time (by as much as 50%) compared to the traditional specification based test methods.

#### Acknowledgments

First and foremost, I would like to thank my advisor Prof. Vishwani D. Agrawal for encouraging me to start on this doctoral program and constantly challenging me to push the limits and seek out bold, new ideas. His enthusiasm for research and learning is infectious, which is something I hope I have picked up and would like to embody in my own life. Big thanks goes out to Prof. Adit Singh and Prof. Foster Dai for serving on my thesis committee, and in each of whose classes, I learned significant material that helped me get a good grounding in the broad areas of VLSI Design and Test. Thanks are due to Prof. Alvin Lim for serving as the external reader on my committee. I owe a debt of gratitude to Prof. Virendra Singh (IIT Bombay, India), whose early interest in my work spurred me to pursue it further, which has eventually come to be my PhD thesis. I should thank members of the analog test community, particularly Haralampos Stratigopoulos (TIMA labs, France), whose comments at various points in time have benefited this work.

Some other professors who I have interacted with closely and learned from are: Prof. Prathima Agrawal through the Wireless Networking seminar series in which I presented at least once and was educated on numerous emerging topics in wireless communication; Prof. Stan Reeves, whose course on digital image processing helped spawn several of my papers in the area of fault tolerant image processing; Prof. Stu Wentworth who offered the Radar Engineering course where he helped us build a radar target model, but in him I saw first-hand how to be a great teacher with a keen interest in the student success.

A word of thanks goes to all my present and past lab colleagues and office mates at Auburn University for making it a fun place to spend long hours each day. Office staff in ECE, namely Mary Lloyd, Shelia Collis and Linda Allgood were particularly helpful throughout my stay in Auburn. Linda Barresi and Joe Haggerty were helpful in procuring components for my experiments in a timely fashion.

I acknowledge the Department of ECE at Auburn University for supporting my studies with generous teaching fellowships; Auburn University Wireless Engineering Research and Education Center (WEREC) for funding several conference travels. I would like to acknowledge Intel Corporation, and my colleagues there, for being particularly supportive of my thesis-writing effort during the last semester of my graduate school that I spent in practical training.

Finally, I would like to thank my extended family for being supportive of all my endeavors. This thesis is dedicated to them.

# Poem by the Author

Working is tricky,

If you choose to be picky!

Research is sucky,

When you try to be finicky!

I knew this already,

But I chose to be heady.

After a while,

I've realized, it was all worthwhile!

I pushed myself to publish many papers,

Even as I wonder if they'll end up in diapers!

I hope many other folks will cite my paper,

Lest I be labeled an academic pauper!

I'm finishing this dissertation,

Without much adoration;

Oh God, my Committee,

Will they approve my Ph.D.?

# Table of Contents

| A  | ostrac  | t                                                                                    | i   |

|----|---------|--------------------------------------------------------------------------------------|-----|

| A  | cknow   | rledgments                                                                           | iv  |

| Li | st of 1 | Figures                                                                              | Х   |

| Li | st of   | Tables                                                                               | xiv |

| 1  | In      | troduction                                                                           | 1   |

|    | 1.1     | What are RF/Analog/Mixed-Signal Circuits?                                            | 1   |

|    | 1.2     | Role of RF/Analog/Mixed-Signal Circuits in Today's Digital World $\ \ldots \ \ldots$ | 2   |

|    | 1.3     | Analog Test Versus Digital Test                                                      | 3   |

|    | 1.4     | Important Challenges in RF/Analog/Mixed-signal Circuit Testing                       | 5   |

|    | 1.5     | A Brief History of RF/Analog Test and Diagnosis                                      | 9   |

|    |         | 1.5.1 Taxonomy of Analog Circuit Fault-Diagnosis Techniques                          | 9   |

|    |         | 1.5.2 Taxonomy of RF/Analog Circuit Test Techniques                                  | 12  |

|    |         | 1.5.3 Efforts on Test Cost Reduction for Analog Circuits                             | 15  |

|    | 1.6     | Contributions of this Thesis                                                         | 16  |

|    | 1.7     | What Lies Ahead?                                                                     | 17  |

| 2  | Sig     | gnature Based Testing of RF, Analog and Mixed-Signal Circuits                        | 18  |

|    | 2.1     | The Need for Circuit Signatures                                                      | 18  |

|    | 2.2     | Attributes of an Ideal Signature                                                     | 18  |

|    | 2.3     | Analog Circuit Testing Based on Signatures: Test Methodology                         | 20  |

|    | 2.4     | Conclusion                                                                           | 22  |

| 3  | Po      | olynomial Coefficients as Test Signatures                                            | 23  |

|    | 3.1     | Introduction                                                                         | 23  |

|    | 3.2     | Preliminaries                                                                        | 27  |

|   |     | 3.2.1 Analysis of Polynomial Coefficients  | 27 |

|---|-----|--------------------------------------------|----|

|   |     | 3.2.2 Definitions                          | 29 |

|   | 3.3 | Problem Description and Sketch of Solution | 29 |

|   | 3.4 | Generalization                             | 32 |

|   | 3.5 | Experimental Results                       | 33 |

|   | 3.6 | Fault Diagnosis                            | 42 |

|   |     | 3.6.1 Computation of Sensitivities         | 43 |

|   |     | 3.6.2 Diagnosing Parametric Faults         | 43 |

|   |     | 3.6.3 Deducing Faults                      | 44 |

|   | 3.7 | Conclusion                                 | 44 |

| 4 | V-  | Transform Coefficients as Test Signatures  | 48 |

|   | 4.1 | Introduction                               | 48 |

|   | 4.2 | Background                                 | 51 |

|   | 4.3 | The V-Transform                            | 53 |

|   | 4.4 | A Problem and an Approach                  | 53 |

|   | 4.5 | Generalization                             | 56 |

|   | 4.6 | Fault Diagnosis                            | 58 |

|   | 4.7 | Simulation Results                         | 59 |

|   | 4.8 | Experimental Verification                  | 62 |

|   |     | 4.8.1 Test Setup                           | 63 |

|   |     | 4.8.2 Measured Results                     | 64 |

|   | 4.9 | Sumamrizing V-Transform                    | 66 |

| 5 | Pr  | obability Moments as Test Signatures       | 67 |

|   | 5.1 | Introduction                               | 67 |

|   | 5.2 | Background                                 | 69 |

|   |     | 5.2.1 Moment Generating Functions          | 69 |

|   |     | 5.2.2 Random Variable Transformation       | 70 |

|    |        | 5.2.3 Minimum Size Detectable Fault                                         | 72  |

|----|--------|-----------------------------------------------------------------------------|-----|

|    | 5.3    | Problem and Approach                                                        | 72  |

|    | 5.4    | Generalization                                                              | 75  |

|    | 5.5    | Fault Detection in Elliptic Filter                                          | 76  |

|    | 5.6    | Fault Diagnosis                                                             | 78  |

|    | 5.7    | Fault Diagnosis in Low Noise Amplifier                                      | 80  |

|    | 5.8    | Conclusion                                                                  | 81  |

| 6  | Во     | ounds on Fault Coverage and Defect Level in Signature Based Testing         | 85  |

|    | 6.1    | Introduction                                                                | 85  |

|    | 6.2    | Problem Formulation                                                         | 87  |

|    | 6.3    | Our Approach                                                                | 89  |

|    |        | 6.3.1 Bounding Defect level                                                 | 89  |

|    |        | 6.3.2 Bounding Fault Coverage                                               | 92  |

|    | 6.4    | Simulation and Computation                                                  | 94  |

|    | 6.5    | Simulation Versus Optimization: A Trade-off                                 | 97  |

|    | 6.6    | Conclusion                                                                  | 99  |

| 7  | Сс     | onclusion                                                                   | 101 |

|    | 7.1    | Thoughts on Future Work                                                     | 101 |

|    |        | 7.1.1 Adaptive Test With Signatures                                         | 102 |

|    |        | 7.1.2 Preliminary Experiments                                               | 102 |

|    |        | 7.1.3 Estimating Defect Level in Analog and Radio-Frequency Circuit Testing | 104 |

| Bi | bliogr | aphy                                                                        | 106 |

| A  | So     | me Theorems on Nonlinear Systems                                            | 116 |

| В  | Οι     | atput Variance of RC Filter                                                 | 119 |

# List of Figures

| 1.1 | Distribution of input/output functions of different types of circuits                                                                                                                                                                                                                                                                                                     | 2  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Hypothetical picture illustrating different blocks that make use of analog/RF modules in a typical RF-SoC (for mobile devices)                                                                                                                                                                                                                                            | 3  |

| 1.3 | Mixed-signal System-on-Chip (SoC) showing size of analog block as a fraction of total die area. Analog interface contributes to about 30% of the total die area. Chip micrograph courtesy of Neolinear [107]                                                                                                                                                              | 5  |

| 1.4 | Mixed-signal System-on-Chip (SoC) showing size of analog block as a fraction of total die area. Analog interface contributes to about 12% of the total die area. Chip micrograph courtesy of Frank Op't Eynde, Alcatel [107]                                                                                                                                              | 6  |

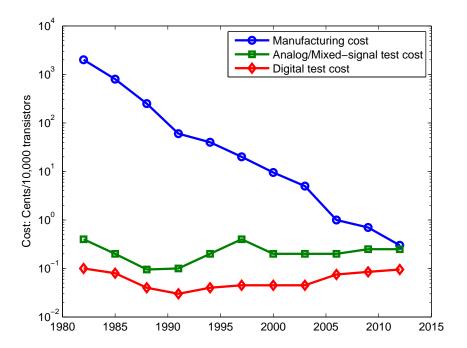

| 1.5 | Manufacturing cost per transistor on a die has steadily decreased, while test cost per transistor has remained almost constant [1, 2]. Around 2014, it is expected that testing a transistor will cost more than manufacturing one. Also of note is that the analog/mixed-signal test cost per transistor is almost 10 times that of the digital test cost per transistor | 7  |

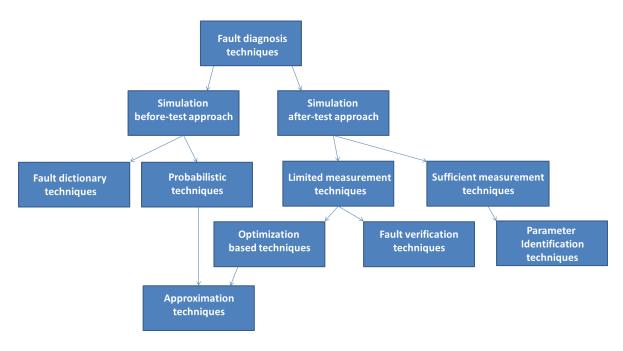

| 1.6 | A possible classification of analog circuit fault-diagnosis techniques [17]                                                                                                                                                                                                                                                                                               | 10 |

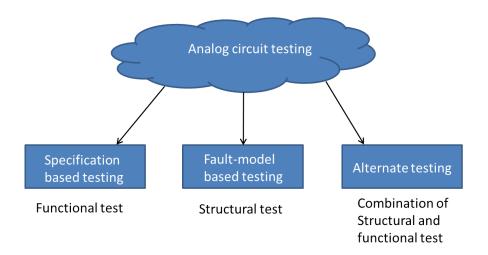

| 1.7 | A possible classification of analog circuit test techniques                                                                                                                                                                                                                                                                                                               | 12 |

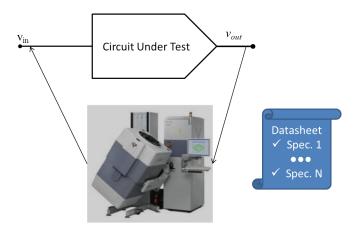

| 1.8 | Specification testing of analog/mixed-signal circuits in a production test setting.                                                                                                                                                                                                                                                                                       | 13 |

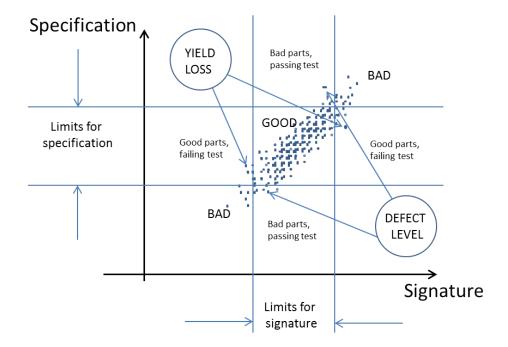

| 2.1  | specification on the Y-axis. An ideal signature will have all points lined up along                                                                       |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | a straight line such that there is perfect correlation between the signature and the specification                                                        | 19 |

| 3.1  | A second order low pass filter                                                                                                                            | 24 |

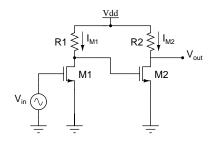

| 3.2  | Cascade amplifier                                                                                                                                         | 25 |

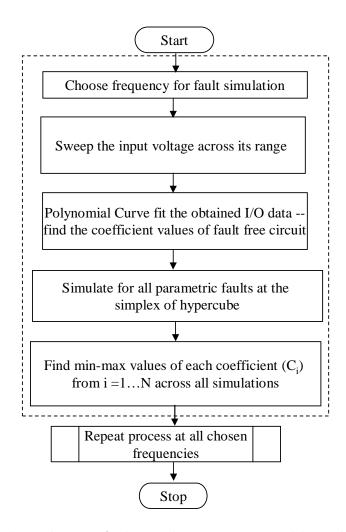

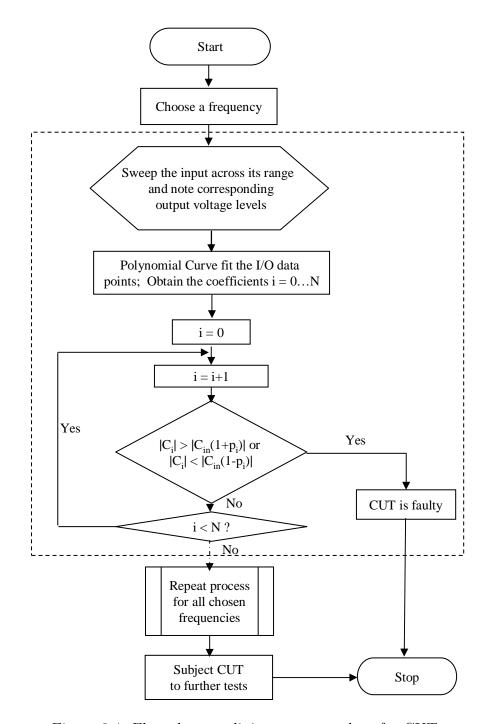

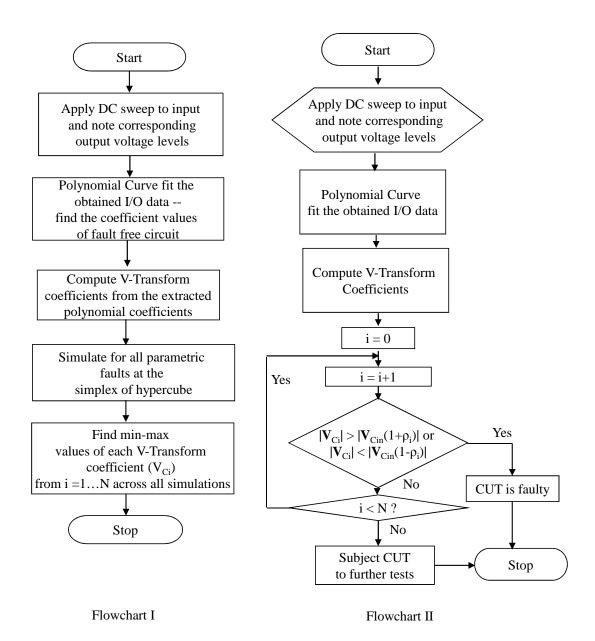

| 3.3  | Flow chart showing fault simulation process and bounding of coefficients                                                                                  | 34 |

| 3.4  | Flow chart outlining test procedure for CUT                                                                                                               | 35 |

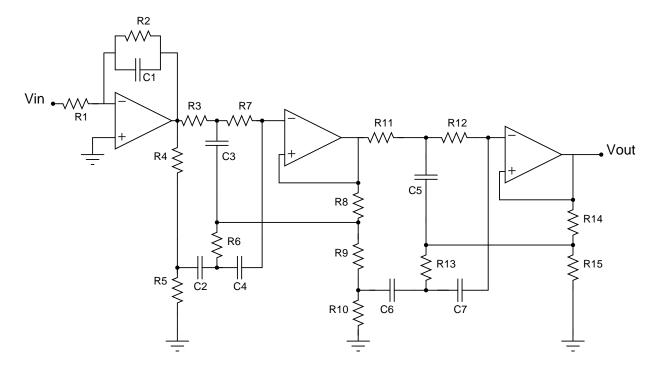

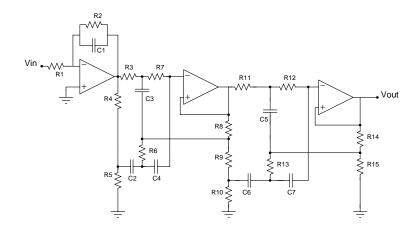

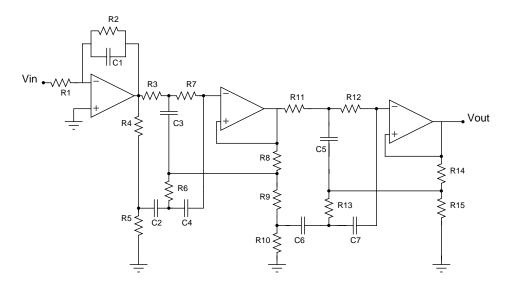

| 3.5  | Elliptic filter                                                                                                                                           | 36 |

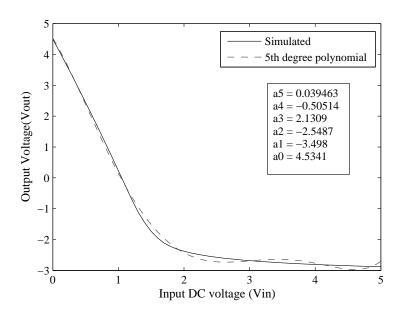

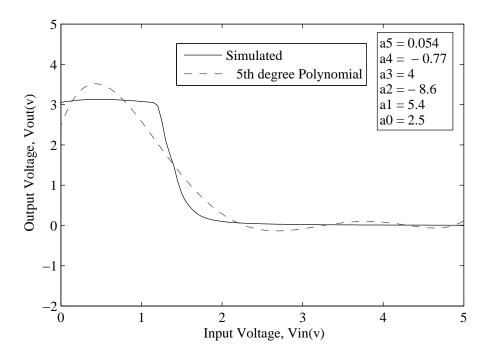

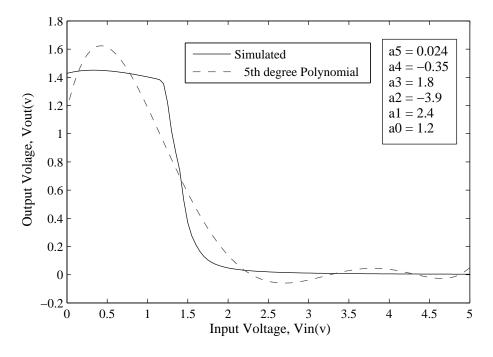

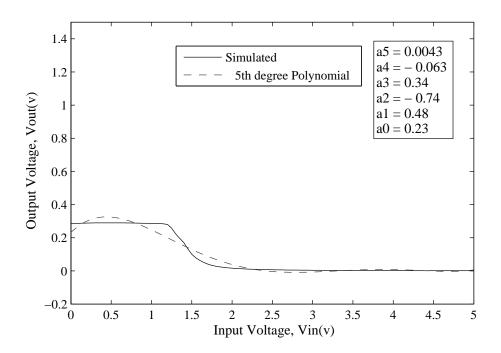

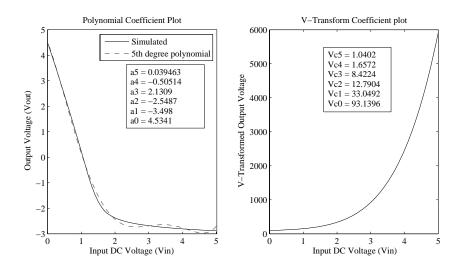

| 3.6  | DC response of elliptic filter with curve fitting polynomial                                                                                              | 37 |

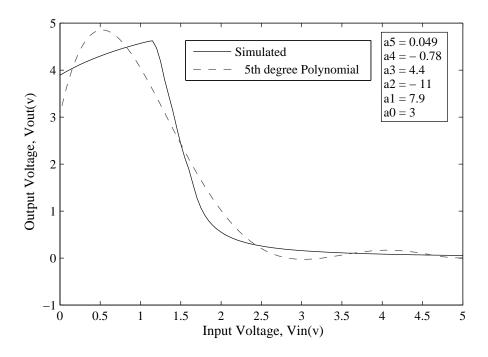

| 3.7  | Curve-fit polynomial with coefficients at frequency = $100 \text{Hz.} \dots \dots$                                                                        | 37 |

| 3.8  | Curve-fitting polynomial with coefficients at frequency = $900$ Hz                                                                                        | 38 |

| 3.9  | Curve-fitting polynomial with coefficients at frequency = $1000$ Hz                                                                                       | 38 |

| 3.10 | Curve-fitting polynomial with coefficients at frequency = $1100$ Hz                                                                                       | 39 |

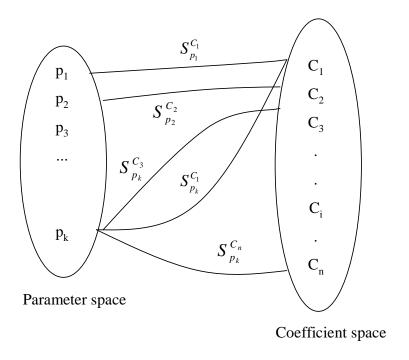

| 3.11 | Mapping showing one possible relation between various parameters and coefficients.                                                                        | 39 |

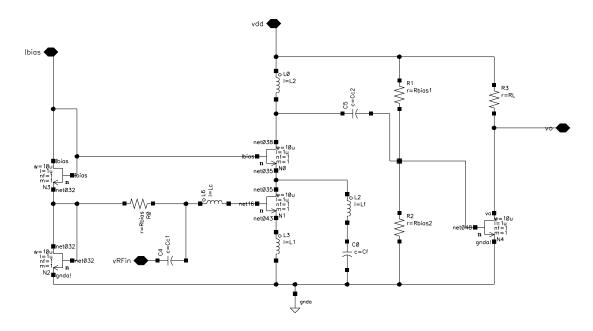

| 3.12 | Low noise amplifier (LNA) schematic                                                                                                                       | 40 |

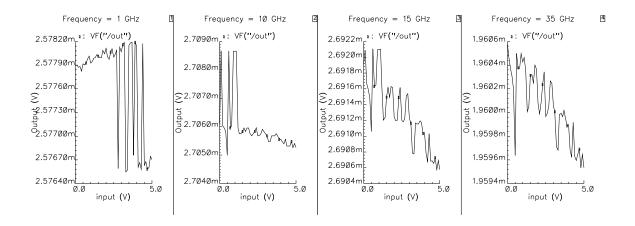

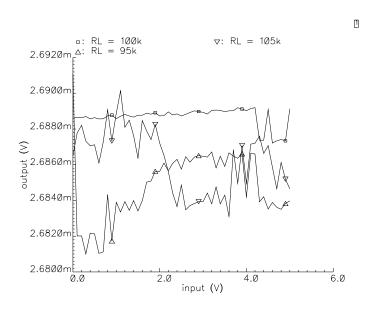

| 3.13 | I/O response of LNA at four frequencies                                                                                                                   | 41 |

| 3.14 | Comparison of I/O plots of LNA at 3 different values of load resistance $R_L = 95\text{k}\Omega$ , $100\text{k}\Omega$ (nominal), and $105\text{k}\Omega$ | 41 |

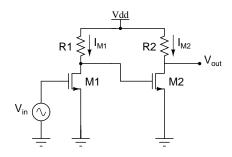

| 4.1  | Cascade amplifier.                                                                                                                                        | 54 |

| 4.2 | test procedure (Flowchart II)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 57 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

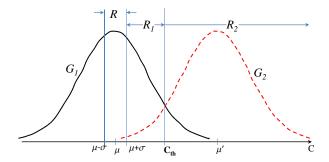

| 4.3 | Probability distribution of polynomial coefficient C under a parametric fault (broken line) as opposed to that with only process variation (solid line)                                                                                                                                                                                                                                                                                                                                                                                                   | 59 |

| 4.4 | Elliptic filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 60 |

| 4.5 | DC response of elliptic filter with curve fitting polynomial and V-transform plot.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 61 |

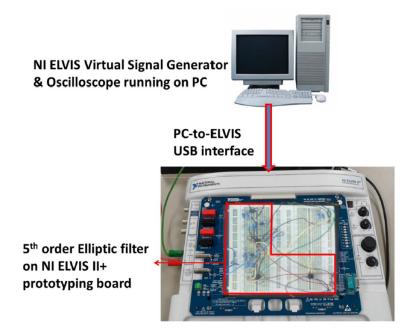

| 4.6 | Test setup with elliptic filter built on the prototyping board, which is in turn mounted on the NI ELVISII <sup>+</sup> bench-top module. Voltage and frequency control of the applied signal is handled through the PC which is connected through USB port to the bench-top module. Output from the circuit is sampled and transferred through the same USB connection to the PC (where it can be post-processed). Also, circuit output can be displayed on the PC using a virtual oscilloscope utility available in the ELVIS software (see Figure 4.7) | 63 |

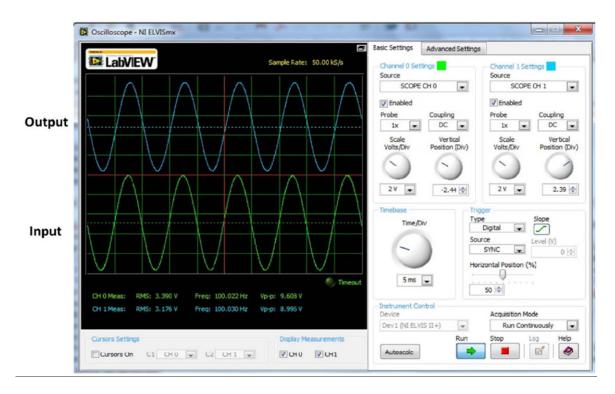

| 4.7 | Input/output, to/from the elliptic filter displayed on the PC based virtual oscilloscope at a frequency $f=100{\rm Hz}.$                                                                                                                                                                                                                                                                                                                                                                                                                                  | 64 |

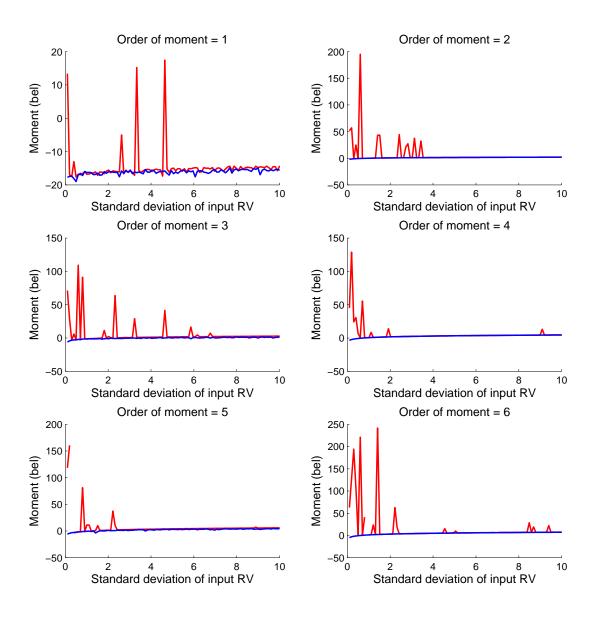

| 5.1 | Moments of different orders as functions of input noise power (standard deviation of input RV) with (in red/dashed) and without (in blue/solid) RV transformation for first order RC filter. See Figure 5.2                                                                                                                                                                                                                                                                                                                                               | 71 |

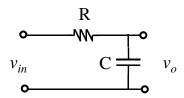

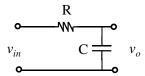

| 5.2 | First-order RC filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 72 |

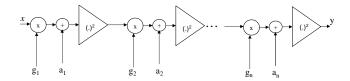

| 5.3 | A cascade amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 73 |

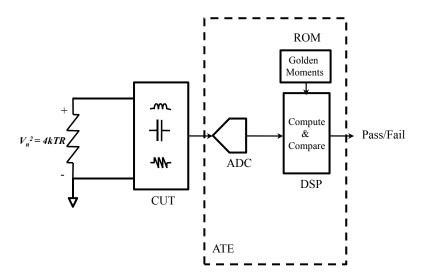

| 5.4 | Block diagram of a system with CUT using white noise excitation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 76 |

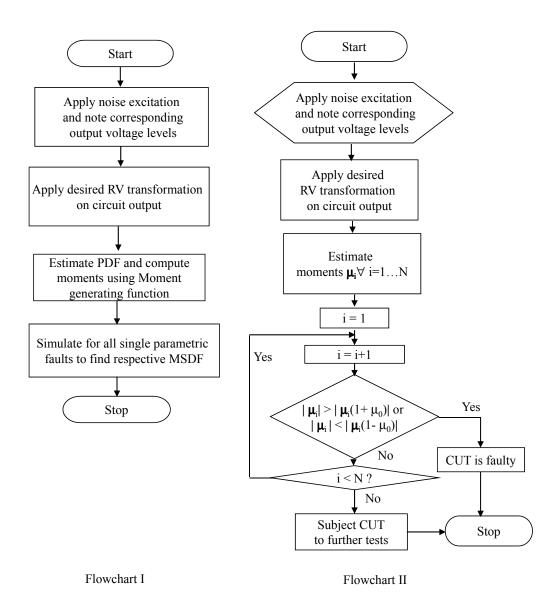

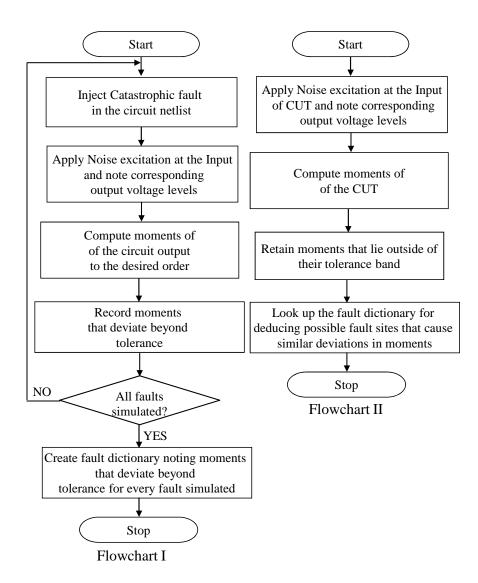

| 5.5 | Fault simulation process and bounding of moments (Flowchart I), and the complete test procedure (Flowchart II)                                                                                                                                                                                                                                                                                                                                                                                                                                            | 77 |

| 0.6 | Elliptic filter                                                                                                                                       | 78  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.7 | Fault simulation (Flowchart I) and Fault diagnosis (Flowchart II) procedures summarized                                                               | 79  |

| 5.8 | Schematic of low noise amplifier                                                                                                                      | 82  |

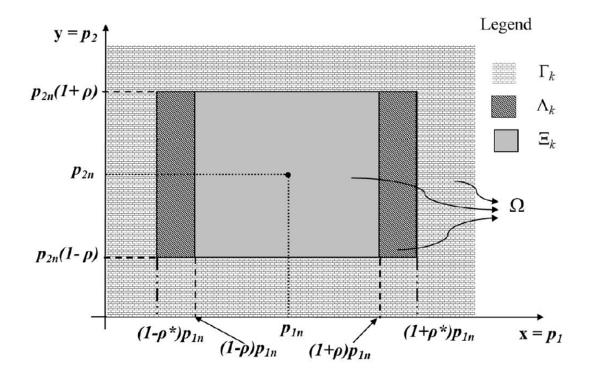

| 6.1 | Hypercube around coefficient $C_k$ and associated regions                                                                                             | 88  |

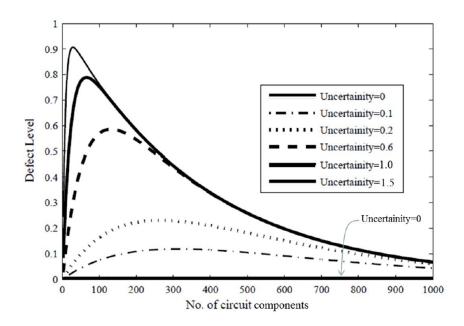

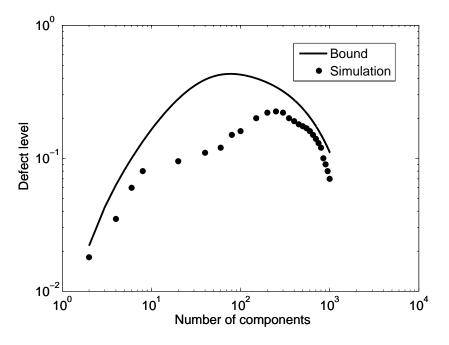

| 6.2 | Defect level (DL) as a function of number of components $(N)$                                                                                         | 95  |

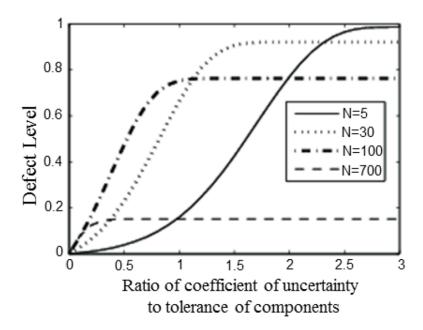

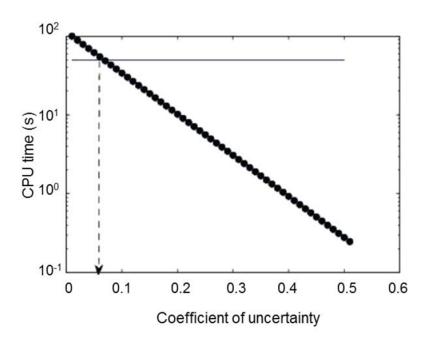

| 6.3 | Defect level (DL) plotted against ratio of coefficient of uncertainty to tolerance of components $(\frac{\epsilon}{\sigma})$                          | 96  |

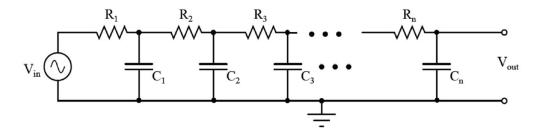

| 6.4 | RC ladder filter network of $\underline{\mathbf{n}}$ stages                                                                                           | 97  |

| 6.5 | Comparison of defect level bounds with simulated value ( $\frac{\epsilon}{\sigma}=0.1$ ) for RC ladder filter network                                 | 98  |

| 6.6 | CPU time (in seconds) to compute NMSDF by simulation versus coefficient of uncertainty, $\epsilon$                                                    | 100 |

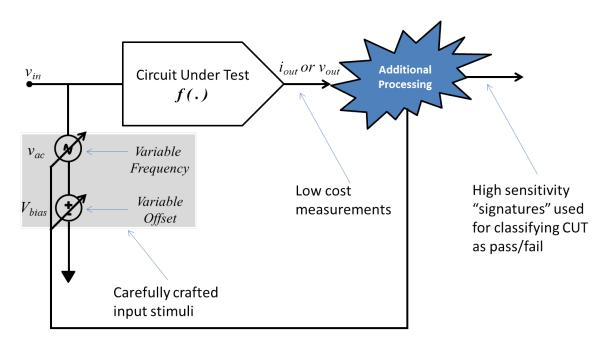

| 7.1 | Block diagram of the adaptive test system based on circuit signatures                                                                                 | 103 |

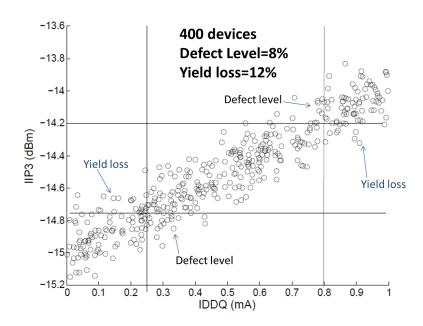

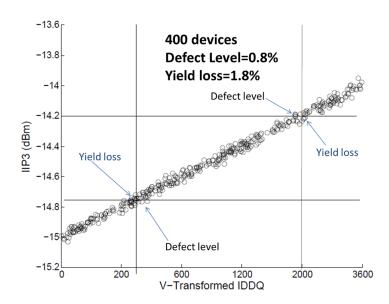

| 7.2 | Scatter plot of tested devices showing defect level and yield loss for the open loop signature test, where the input stimulus is not tuned adaptively | 104 |

| 7.3 | Scatter plot of tested devices showing defect level and yield loss for the closed loop signature test, where the input stimulus is tuned adaptively   | 105 |

| A.1 | A possible system model for a non-linear circuit                                                                                                      | 117 |

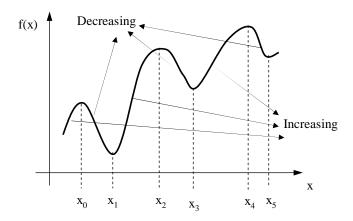

| A.2 | Non-linear, non-monotonic function decomposed into piecewise monotonic functions                                                                      | 118 |

| B.1 | First order RC low-pass filter                                                                                                                        | 119 |

# List of Tables

| 3.1 | MSDF for cascade amplifier of Figure 3.2 with $\alpha = 0.05$                                                               | 32 |

|-----|-----------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | LNA specification                                                                                                           | 40 |

| 3.3 | Parameter combinations leading to maximum values of coefficients with $\alpha=0.05$ for the LNA                             | 42 |

| 3.4 | Parameter combinations leading to Min values of coefficients with $\alpha=0.05$ for the LNA                                 | 43 |

| 3.5 | Parameter combinations leading to Max and Min Values of coefficients with $\alpha = 0.05$ at 1000Hz for the elliptic filter | 45 |

| 3.6 | Results of some injected faults at different frequencies for the elliptic filter                                            | 46 |

| 3.7 | Parametric fault fiagnosis with confidence levels of $\approx 98.9\%$ for the elliptic filter.                              | 47 |

| 3.8 | Results of test and diagnosis of some injected faults for LNA                                                               | 47 |

| 4.1 | MSDF for cascade amplifier of Figure 4.1 with $\alpha = 0.05.$                                                              | 56 |

| 4.2 | Parameter combinations leading to maximum values of V-transform coefficients with $\alpha = 0.05$ for the elliptic filter   | 60 |

| 4.3 | Parameter combinations leading to minimum values of V-transform coefficients with $\alpha=0.05$ for the elliptic filter     | 61 |

| 4.4 | Results for some injected faults in the elliptic filter                                                                     | 62 |

| 4.5 | Parametric fault diagnosis with confidence levels of $\approx 88\%$ for the elliptic filter.                                | 62 |

| 4.6 | Measured results for some injected faults in elliptic filter                                                                | 65 |

| 5.1 | MSDF for cascade amplifier of Figure 5.3 with $\mu_0 = 0.05$                                                                | 75 |

| 5.2 | Parameter combinations leading to maximum values of moments with device tolerance $\gamma = 0.05$ in elliptic filter.       | 80 |

| 5.3 | Parameter combinations leading to minimum values of moments with device tolerance $\gamma = 0.05$ in elliptic filter                                                                                           | 83  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.4 | Fault detection of some injected faults in elliptic filter                                                                                                                                                     | 83  |

| 5.5 | Fault dictionary for catastrophic faults in low noise amplifier                                                                                                                                                | 84  |

| 6.1 | Defect level and fault coverage of benchmark circuits obtained from computation and simulation. For brevity in the table, T: Transistor, O: Opamp, R: Resistor, C: Capacitor, $N$ : Total number of components | 98  |

| 7.1 | Comparison of defect level, yield loss, and test time for actual specification test, signature test in open loop, and signature test in closed loop.                                                           | 103 |

#### Chapter 1

#### Introduction

# 1.1 What are RF/Analog/Mixed-Signal Circuits?

"RF/Analog/Mixed-signal" is a label associated with circuits that have a portion of their operating input, or output, or both input and output, consisting of continuous-time, continuous-amplitude signals, as opposed to digital circuits that have both their operating input and output consisting of discrete-time, quantized-amplitude (Boolean) signals.

RF circuits can be broadly classified as circuits that process signals in the high-frequency (ranging from a low of 20 kHz all the way up to 60 GHz or higher) domain. Examples include low noise amplifier (LNA), mixer, filter, and voltage controlled oscillator among others.

Analog circuits are a bigger class of circuits, in that, they encompass all continuous-time, continuous-amplitude signal processing circuits. As such RF circuits can be thought of as a subset of analog circuits operating in the high-frequency range [103]. Examples include dc power supply circuits such as regulators, op-amps, and signals conditioning circuits.

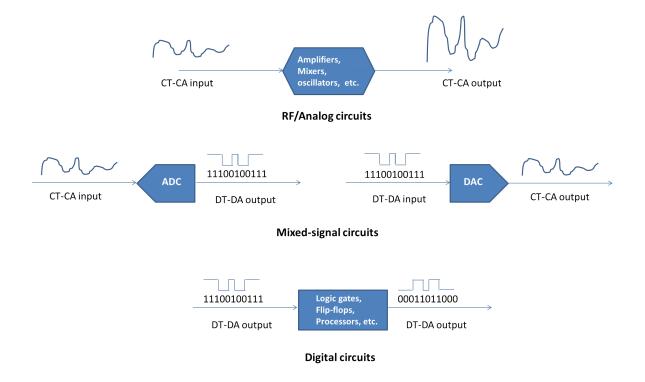

Mixed-signal circuits are those that function as a bridge between the digital and the analog worlds, in that one of their operating input (output) is continuous-time, continuous-amplitude (known as analog) signal, while the output (input) is discrete-time, discrete-amplitude (known as digital) signal. Examples include analog-to-digital converters (input = analog, output = digital), and digital-to-analog converters (input = digital, output = analog). Digital circuits have both their inputs and outputs in the discrete-time discrete-amplitude domain. Figure 1.1 illustrates the input/output domain distribution of RF/analog/mixed-signal and digital circuits with example circuits for each type.

Figure 1.1: Distribution of input/output functions of different types of circuits.

# 1.2 Role of RF/Analog/Mixed-Signal Circuits in Today's Digital World

The nature of information produced in the world around us is analog, that is, the myriad information sources—such as sensors, be it video, audio, heat, light, or radio frequency (RF)—generate signals in a continuous-amplitude, continuous-time fashion. On the other hand, today's computing is leveraging the digital microprocessor revolution where most computation happens digitally in a large monolithic piece of silicon. Consequently, any processing of these signals calls for a bridge between the analog and digital worlds. Analog-to-digital converter (fittingly named) is a typical circuit that functions as a bridge. There are many other analog circuits needed before the signal becomes bridgeable like signal-conditioning circuits that make use of amplifiers, filters and so on.

Similarly, the radio waves transmitted in free air by today's ubiquitous cell-phones are relayed by virtue of those waves being high-frequency analog signals [74]. At the transmitting as well as the receiving end of such a wireless communication system, processing

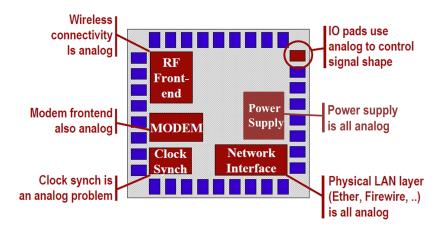

Figure 1.2: Hypothetical picture illustrating different blocks that make use of analog/RF modules in a typical RF-SoC (for mobile devices).

(coding/decoding) of radio signals is accomplished by several RF or analog circuit blocks such as low noise amplifiers, phase-locked loops, mixers, and filters [104].

Analog amplifiers are also used at the digital chip boundaries acting as buffers to drive the pins with adequate amounts of current [50]. Direct-current (dc) power-supply required to power digital or analog circuits are composed of analog circuitry. Virtually any system-on-chip (SoC) or custom integrated circuit conceivable ends up having a portion of analog circuitry for accomplishing one or more of the tasks noted above. In other words, analog is everywhere in todays digital world. Figure 1.2 shows the RF/analog circuit portions in a typical RF-SoC of today. Notice that RF/analog circuits contribute to roles from powering up the chip to enabling communication with the external world.

#### 1.3 Analog Test Versus Digital Test

Digital circuits have succinct fault models (like the stuck-at fault) allowing the use of "structural" tests that target specific faults instead of testing for the entire functionality of the circuit. They serve as effective replacements of functional tests, thereby obviating long test times that would have otherwise been necessary for running functional tests even on a moderately-sized digital circuit. Consider for example an *n*-input, *m*-output, *g*-gate

digital circuit (without memory elements like flip-flops); testing such a circuit exhaustively for functionality can take  $2^n$  vectors in the worst-case [33]. Clearly the number of vectors needed to test the circuit is exponential in the number of inputs in the circuit. On the other hand by targeting faults individually (based on a fault model), the number of test vectors needed to test the complete circuit is bounded by the number of faults to be targeted. For this example, it is of the order of m + n + g. Consequently, fault model based tests considerably reduce the number of test vectors needed when compared to functional tests for large digital circuits. Common structural defects (e.g., signal line short to power and/or ground rails or other signal lines) in integrated circuits are easier to model as faults in digital circuits due to the fact that the deviant behavior in the presence of a fault can be defined concisely (for example, as an incorrect logic value, of which there are only two possibilities—1 or 0) at any node in the digital circuit. This simplicity in fault-modeling is an important factor contributing to the prevalence of structural testing in digital circuits.

In contrast, analog circuits propagate signals through them in a continuum of signal values, requiring a large number of test signals to test the circuit. The deviant behavior in a faulty analog circuit can take a whole spectrum of incorrect values. For example, if the acceptable range of voltage at some node in an analog circuit is  $[V_{nom} - V_{tol}, V_{nom} + V_{tol}]$ , then the faulty behavior can take a whole spectrum of values outside this nominal range. One possible fault model for this situation could be to have a resistor tied to the supply rail and changing the value of that resistor to emulate the incorrect spectrum of voltage values. Unfortunately, there is no one resistance value (or fault-size) that can change the voltage at the node to all incorrect values in the spectrum.

A number of resistor values have to be used to sample the faulty voltage spectra sufficiently. So a large number of fault-injections may be necessary to model a fault even at a single node of an analog circuit. This complexity of fault models makes the model-based testing of analog circuits an unsuitable proposition. The prevalent practice in the industry is to use a large set of signals to functionally qualify or test the circuit. Applying these test

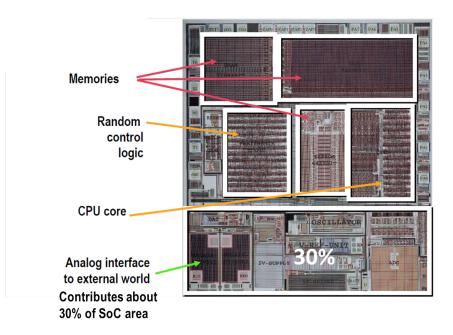

Figure 1.3: Mixed-signal System-on-Chip (SoC) showing size of analog block as a fraction of total die area. Analog interface contributes to about 30% of the total die area. Chip micrograph courtesy of Neolinear [107].

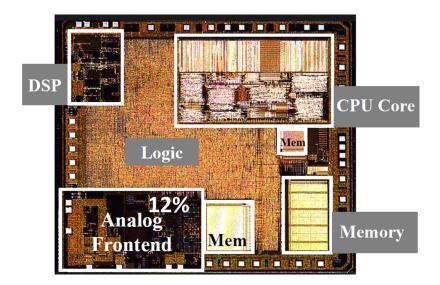

signals to test analog circuits can take disproportionately large amounts of time. An oftenquoted number is that analog test take as much as 50% of the total test-time in spite of the analog circuitry occupying less than 15% of the die-area [2]. See for example the micrographs of two mixed-signal system-on-chip (SoC) integrated circuits shown in Figures 1.3 and 1.4. Both have fairly complex analog features, yet the analog circuit size is no greater than 30%.

# 1.4 Important Challenges in RF/Analog/Mixed-signal Circuit Testing

Previous sections show that analog circuits find their way on almost every systemon-chip type of integrated circuit besides dedicated custom-analog circuits. Heterogeneous integration, increasing wafer sizes, and very fine device geometry have contributed to an increase in analog circuit failure modes that can be harder to catch, degrade the circuit specification in ever more subtle ways, and impact revenue with higher defect level and consequent customer returns. Added to that, innovations in test technology have not kept up with the decreasing manufacturing cost per transistor. As can be seen in the plot in

Figure 1.4: Mixed-signal System-on-Chip (SoC) showing size of analog block as a fraction of total die area. Analog interface contributes to about 12% of the total die area. Chip micrograph courtesy of Frank Op't Eynde, Alcatel [107].

Figure 1.5, test cost has remained fairly constant with the passing of years, while the cost of manufacturing a transistor has dropped steadily [1]. Furthermore, though analog circuits contribute less than 10-20% of the chip area, they account for over 50% of the test cost [2]. This can also be noticed in from the plot in Figure 1.5 where the analog test cost per transistor is almost an order of magnitude higher than digital test cost per transistor.

Test cost stemming from long test-times on expensive ATE is the underlying theme of important test problems in analog/mixed signal circuits.

Non-linear, continuous-time, continuous-amplitude nature of analog circuits:

Most analog circuits are non-linear, continuous-time, and continuous amplitude in nature and that makes it a computational challenge to both implement automatic test generation algorithms, and store the large amounts of waveform data that is to be

Figure 1.5: Manufacturing cost per transistor on a die has steadily decreased, while test cost per transistor has remained almost constant [1, 2]. Around 2014, it is expected that testing a transistor will cost more than manufacturing one. Also of note is that the analog/mixed-signal test cost per transistor is almost 10 times that of the digital test cost per transistor.

# 2. "Functionally-good-enough" testing does not cut the deal:

Testing if a circuit is good-enough (or functional) for some specifications can be relatively easy, but extracting the absolute value of that specification can involve significantly higher effort. For example, in specification testing an RF transceiver, the circuit can be qualified as good if it passes a simple loop-back test. In a loop-back test, the transmitter is tied back to the receiver and the transceiver is considered "pass," if it meets all the receiver specifications, but to make sure that its specifications meet all the regulatory compliance requirements and binning it within a performance bin can be more difficult. Further not all wireless standards permit concurrent operation of transmit and receive modes in a transceiver (which is a prerequisite for loop-back test), and designing the circuit enable this capability can involve major design effort and consequent cost.

3. Inadequate signal visibility at the circuit output:

Analog circuits for specific functions can be small and deeply embedded within a larger circuit. Bringing out these signals to the pads without degrading the signal quality can be a challenge. Further the measurement inaccuracies due to noise (and consequent lack of repeatability) may call for longer measurement times to average out any noise induced errors. Such measurement errors due to noise is uncommon in digital circuits due to the inherent noise margins.

4. Process variation has made life difficult not only for designers, but also for test engineers:

Random manufacturing process variation can have significant impact on analog performance parameters. This is because analog circuits are designed with stringent matching requirements (for example, transistors in both the legs of a current-mirror circuit [50, 51] should be a replica of each other lest we risk a high offset current in one branch and the resulting non-linearity if the circuit were to be used in an amplifier). Traditionally testing for sizable manufacturing defects has been the primary concern during test. With process variation induced local variation of circuit parameters, distinguishing between random process variations and recurring small manufacturing defects can be difficult if the deviation in nominal functional performance and defective circuits is small. This is an important concern in analog circuits much like the problem encountered in distinguishing small-delay faults from process variation induced delay faults in digital circuits.

In the next section, we review the efforts spent on RF/Analog circuit testing and diagnosis since the early second-half of the twentieth century.

# 1.5 A Brief History of RF/Analog Test and Diagnosis

Majority of the circuits before the 1960s were analog. These circuits were usually made with discrete components on printed-circuit-boards. There were minimal, if any, monolithic integrated circuits. The traditional research focus was not as much on testing these circuit boards as it was on diagnosis of faulty components on the circuit board. The challenge traditionally lay in determining which component was at fault, so that the broken circuit could be fixed by replacing the faulty component causing the faulty output. This was so because integrated circuits were still nascent, and it was expensive to discard the entire circuit board instead of replacing the few faulty components. The premise was that if there are any circuits that are bad, it is probable that the faulty components could be identified based on certain uniquely associable attributes of the outputs to the components in the circuit. Many researchers [17, 19, 46, 62, 64, 73, 87, 144, 150] proposed several unique and interesting solutions to the diagnosis problem, which is essentially a fault localization problem. In addition, researchers have also worked on the fault-prediction problem [11, 108, 109, 149], where the circuit output is continuously monitored to predict if any of the circuit-components are about to fail, so they can be replaced in advance of an actual failure. Clearly faultprediction is a more challenging problem than fault-diagnosis. We will first examine the different fault-diagnosis techniques that have been proposed in literature.

#### 1.5.1 Taxonomy of Analog Circuit Fault-Diagnosis Techniques

Several different criteria could be used for categorizing fault-diagnosis techniques. The popular method of classification is based on the stage in the testing at which simulation of the circuit is undertaken [97, 106, 110]:

- Simulation-before-test, and

- Simulation-after-test.

Figure 1.6 [17] shows a taxonomy of fault-diagnosis techniques based on the above criteria.

Figure 1.6: A possible classification of analog circuit fault-diagnosis techniques [17].

#### Fault Dictionary Based Diagnosis

Fault-dictionary techniques classified under simulation-before-test techniques in Figure 1.6 are similar to the widely used fault-dictionary based diagnosis approaches for digital circuits [7, 33]. The first step is to define the most likely faults that can be expected in a given circuit. Defining faults is an important step as the dictionary-size is limited by number of faults defined. An appropriate number of test responses are then captured by simulating the circuit-under-test (CUT) by injecting the defined faults one-by-one, such that unique identification of each fault can be possible by deductive reasoning based on the captured responses for all the applied tests before actually subjecting the circuit in question to test. At the time of test, the captured responses are used to identify the fault or localize it to a small 'ambiguity-set' of faults. The test responses can be captured in frequency domain [31, 88, 89, 133, 148] or in the time domain [113, 132, 147], or as a combination of both [78, 114].

# Diagnosis Based on Parameter Identification Techniques

Parameter identification techniques, grouped under simulation-after-test approach in Figure 1.6 involves estimating the deviation in nominal values of circuit components based on voltage/current measurements made at specific nodes in the circuit-under-test for a known input response. The nominal component values and topology of circuit-under-test is known a priori. The deviations in the component values from their nominal values is uniquely determined by solving the set of linear or non-linear equations of the circuit (as determined by the circuit topology). Such circuits for which component values are uniquely determinable based on a few measurements are said to be element-value-solvable [20, 21, 22] circuits and are amenable to parameter identification techniques.

# Diagnosis Based on Fault Verification Techniques

Fault verification techniques are based on the premise that for a circuit of  $n_c$  components, with  $n_m$  measurements taken at test, all the faulty elements ( $n_f$  in number) can be uniquely identifiable if  $n_f$  is very small, such that the inequality  $n_f \ll n_m \ll n_c$  is satisfied. The faulty elements are identified by checking the consistency of certain equations which are invariant on the changes in the faulty component values [49, 69, 105, 146].

#### Approximation Techniques for Diagnosis

Approximation techniques are able to localize faults with limited number of measurements. Two prominent types of approximation techniques are probabilistic [30, 71] and optimization-based [60, 81, 102]. In probabilistic diagnosis techniques all the circuit fault-simulation is done before test and can be classified under simulation-before-test. Their working principles are very similar to the dictionary based approach. Optimization techniques, on the other hand, optimize some pre-determined criterion to find the most likely faulty element. For example, the  $L_2$  approximation technique [81, 102] uses weighted least squares

Figure 1.7: A possible classification of analog circuit test techniques.

criterion in identifying the—most-likely faulty element—the element that has undergone the largest deviation from its nominal value.

However, with the advent of integrated circuits, things began to change. Cost of manufacturing even complex circuits, with fairly large component counts, was cheaper than building the bulky boards. The focus slowly shifted from finding the faulty component, or diagnosis, to finding out if the overall circuit behaved as it was designed to behave. We will now examine taxonomy of efforts in analog circuit testing that are geared towards different aspects of the test problem, all of which can be either categorized as aiming to reduce the analog test cost, or increase the testability of the circuit and test-quality.

# 1.5.2 Taxonomy of RF/Analog Circuit Test Techniques

Figure 1.7 shows the taxonomy of test techniques for analog/RF circuits. The different analog test techniques that are proposed in literature can be classified under three broad categories: functional, structural, and alternate (combination of functional and structural) testing. We shall now review each of the categories and sampling of different test techniques that have been proposed under each of those categories.

Figure 1.8: Specification testing of analog/mixed-signal circuits in a production test setting.

#### Specification-Based Testing

The traditional and widely prevalent approach to analog/RF test has been to test the circuit specifications against a list of acceptable limits for each of those specifications. The circuit is deemed to be "Pass," if all its specifications are within the acceptable limits; else it is considered "Fail". Figure 1.8 shows an illustrative picture of how specification based testing is carried out in a production test setting. This approach, though widely prevalent, is expensive even for a pass/fail type of test. The higher test cost stems from large amounts of input stimulus to be applied on the circuit-under-test for measuring all the specifications contributing to the test time on expensive test equipment [32, 79, 91, 112]. In addition, there is the simulation overhead to develop the input stimulus needed for production testing of all specifications [66, 82, 153].

#### Fault-Model Based Test Techniques

In fault-model based test techniques, the primary objective is to abstract the many physical defects that occur in manufacturing into its electrical equivalent such that tests can target these faults instead of the circuit specifications. The expectation is that testing for these faults will sufficiently cover all the specifications and will do so in a shorter time than the time required for testing the specifications themselves. Typical fault models for analog circuits are component opens and shorts that mimic large defects that can significantly deviate the behavior of the component. Such faults are known as catastrophic faults. Examples of catastrophic faults can be resistor open or short. Defects that lead to small deviations in functionality of the circuit components are modeled as fractional drifts from the nominal values of the circuit element (usually beyond the component tolerance limit), and are called parametric faults or soft faults. Examples of parametric faults can be  $\pm 10\%$  deviation in the nominal value of the resistor. Number of such fault models have been developed for different components in analog circuits [141]. Different fault-model based test schemes [29, 36, 53, 55, 57, 58, 80, 90, 100, 101, 130, 131] have been proposed in literature. We briefly discuss a representative set of these techniques.

Sensitivity based test and diagnosis techniques [57, 58, 129] constitute testing circuit specifications using the sensitivity of the specifications to components in the circuit. The sensitivity,  $S_p^C$ , of a circuit-specification, C, to a circuit-component, p, is defined as:

$$S_p^C = \frac{\frac{\delta C}{C}}{\frac{\delta p}{p}} \tag{1.1}$$

This sensitivity of specifications to the circuit components is leveraged to both test and diagnose the circuit for component faults. Whenever a circuit component undergoes deviation from its nominal, fault-free value, multiple circuit specifications can be tracked, and along with the sensitivity matrix relating the specifications to the circuit components, the most likely circuit component at fault can be determined.

Transfer function based testing [53] proposes the use of modeling the circuit in the frequency domain through the transfer function of the circuit's output with respect to its input. By using a frequency rich input signal, the transfer function of the circuit-under-test is estimated. This transfer function is then compared with the ideal circuit transfer function and any deviation in the coefficients of transfer function beyond an acceptable threshold is treated as a "fail," and a full conformance of all coefficients to pre-determined limits on

the coefficient values is treated as a "pass." The acceptable limits on the coefficients are determined by evaluating the coefficients at different fault sizes of the circuit components.

#### Alternate Test Techniques

Alternate test techniques [56, 151, 156, 154] combine the prowess of fault-model based testing with specification-based testing, in that, they target certain key circuit variables such as currents and voltages (commonly referred to as circuit-signatures) at critical nodes instead of the actual specification, yet they deliver a go/no-go judgment on the circuit-under-test based on whether or not the CUT meets all the specification limits set in the data-sheet. Chapter 2 discusses this approach in detail and we reserve this discussion until then.

#### 1.5.3 Efforts on Test Cost Reduction for Analog Circuits

# Test Re-ordering

Test re-ordering involves changing the sequence of specification tests in order to optimize the test sequence for some predetermined objective. Test sequence can be optimized to reveal the failure modes of the devices, which may be helpful early in the production test setting for yield ramp up by identifying the most common causes of failure and fixing them [83, 85]. As the process flow matures, an objective to be optimized for is the test-time since test-time (the time spent by DUT on an expensive ATE) is an important contributor to the overall production test cost [25].

#### **Redundant Test Elimination**

Production test cost is primarily due to the long test-times (stemming from the longinput stimuli) needed for RF/analog devices. With specification tests, where different specifications are tested for in sequence, there is a possibility of dropping certain specifications that may subsume other specifications. For example in case of an ADC testing if the integral non-linearity (INL) specification is  $\pm 0.5$  LSB and differential non-linearity (DNL) specification is  $\pm 1$  LSB, then there is no need for a separate code sweep measurement for DNL specification testing. Eliminating tests for such redundant specifications has been proposed in [84]. Similarly, depending on the chip fall out data from the failed chip statistics, one may be able to leverage the tests that uncover the most defects or fail the most chips. Keeping such tests in the test flow helps retain the quality of the shipped parts while cutting out unnecessary tests that do not add value to the test flow. Techniques based on statistical analysis to eliminate redundant tests for analog and mixed-signal circuits have been proposed in [24, 25].

# DfT Efforts in the Analog/Mixed-Signal Test Domain

As predicted in the test/manufacturing cost curve shown in Figure 1.5, over the years, the cost of putting a transistor on the die has gone down exponentially and is converging with the cost of testing one. It is predicted that the future cost of circuits will be limited by its test cost. This has led to the explosion of techniques to drive the test cost lower by adding extra hardware on the chip such that the manufacturing cost incurred in the process is offset by the test cost savings. Several researchers have developed design-for-test (DfT) techniques needed to address this problem. The most prominent industry-wide DfT for analog portions in a mixed-signal SoC is the IEEE standard analog bus for test access to analog blocks in a DUT. Literature on DfT other than test access for analog and mixed signal circuits has primarily been on built-in self test schemes for ADC/DAC [14, 145].

#### 1.6 Contributions of this Thesis

The principal problem addressed in this thesis is that of designing high-sensitivity circuit-test signatures that are capable of uncovering both parametric and catastrophic faults in RF/analog/mixed-signal circuits. In addition, the proposed signatures have high correlation with specifications of the circuit so that these circuit-signatures can replace actual

circuit specifications as is the practice in alternate test framework for RF/analog and mixed-signal circuits. Further, these signatures have been demonstrated to work well for diagnosis of faulty circuit elements. Finally, bounds on the defect level and fault coverage achievable while using these signatures is theoretically evaluated and validated through simulations on a number of benchmark RF/analog circuits.

# 1.7 What Lies Ahead?

Chapter-wise summary of the thesis is as follows. First chapter provided an introduction to the analog test problem, important challenges today in this area, and the existing methods in the literature. In the second chapter, entitled "Signature Based Testing of RF, Analog and Mixed-Signal Circuits," we take a closer look at the use of signatures in lieu of actual specifications. This chapter forms the basis of the remaining chapters in the thesis which builds on the notion of signatures, thereby proposing stronger and better ones as we go try to increase their sensitivity and correlation to specification measurements. In Chapter 3, we introduce polynomial coefficients of the circuit function which are used as signatures in a closed-form sense to build a model that can accurately detect parametric faults (also known as soft faults). Chapter 4 describes an enhanced sensitivity transformation on polynomial coefficients called V-transform that can deliver almost confidence levels of up to 98% in the detected parametric faults. Chapter 5 discusses an alternate signature that needs little or no input signal design effort. It leverages moments of the probability distribution at the output to uncover faults that are otherwise hidden. It uses a simple distribution function of the input. Chapter 6 provides a formulation, with examples to compute upper bound on the defect level and lower bound on the fault coverage achievable in signature-based test methods. We draw conclusions in Chapter 7, with some thoughts forward-looking ideas that can further enhance the correlation of circuit-signatures to specification through adaptive testing.

#### Chapter 2

Signature Based Testing of RF, Analog and Mixed-Signal Circuits

# 2.1 The Need for Circuit Signatures

In a conventional specification based test methodology, as we saw in the previous chapter, the circuit is classified as "good" or "bad" depending on whether it conforms to the designed specifications listed on the data-sheet. To make the measurements on these circuits, expensive instrumentation is needed and devices end up spending considerable amounts of time on these expensive instruments. Circuit signatures circumvent this problem by eliminating the need for measuring the circuit specifications themselves. Instead, signature based testing seeks to replace expensive specification measurement with a direct measurement that is low-cost, in that, it either does not need expensive instrumentation or can be measured in a fraction of the time required to make a full-specification measurement on an expensive tester. Examples of circuit signatures include the supply current drawn by the circuit for a pre-determined input [10], the temperature at specific neighborhoods of the circuit [5], output voltage envelope [155, 156], the spectral coefficients of the supply current and voltage, and a combination of one or more of these [18].

#### 2.2 Attributes of an Ideal Signature

Good signatures are required to be able to replace specification measurements. But the buyer of an integrated circuit is interested in the specification of the part being purchased. So an indirect measurement or signature that seeks to replace specification should be a very good replacement of the circuit-specification. This means, the correlation of the circuits chosen signature to the actual specification should be very good. Further, for signatures to

Figure 2.1: Scatter plot of measurements showing the signature on the X-axis and the circuit specification on the Y-axis. An ideal signature will have all points lined up along a straight line such that there is perfect correlation between the signature and the specification.

be practically useful, it should be possible to extract them in a production test setting within a fraction of the time required to extract the actual specification measurements themselves. We now briefly go over each of these attributes:

- 1. High sensitivity signatures detect sufficiently small parametric faults, thus augmenting existing fault model based test schemes. Signatures should be sensitive to changes in component values beyond their tolerance range. This will ensure they signatures are capable of detecting small parametric faults that are the result of local process variations.

- 2. High correlation with circuit specifications augmenting alternate circuit test schemes. Signatures are expected to replace actual circuit specifications, so they should be as accurate as possible in predicting the specifications. The more accurate the capability of the signature, the smaller is the yield loss and defect level. Figure 2.1 shows the

scatter plot where the points lined up together (resulting from good correlation between specification and signature) will lead to fewer parts misclassified.

- 3. Small area overhead requires little additional hardware on chip for production testing.

- 4. Large number observables handy in diagnosis.

- 5. Suitable for large class of circuits there are a variety of classes of analog circuits and the concerned test scheme should be amenable to all of them.

- 6. Aids distinction of small defects from process variation (PV) induced faults current need in advanced technology nodes.

- 7. Amenable to self-test building structures on the circuit, and using signatures that aid in testing the circuits themselves can speed-up the test process as all the fabricated dies can be tested in parallel.

# 2.3 Analog Circuit Testing Based on Signatures: Test Methodology

#### 1. Selecting good signatures

The choice of test signatures can be a significant factor in the efficacy of the signature test scheme for testing any circuit. A signature that is capable of capturing most specifications over a wide range of values will ensure high test quality, i.e., a test that results in low defect level and yield loss.

# 2. Designing good input signals

Input signals that bring out all the circuit characteristics are important for ensuring that the signatures serve as a good replacement to the circuit specification. In fact, the combination of input signal and output signature works in tandem to provide the needed robustness for replacing an actual circuit specification with the circuits signature.

#### 3. Monte-Carlo circuit simulation

Circuit components can vary about their nominal values; it is important that the signature chosen have good correlation to the specification over the variation range of the component. Heuristically chosen limits for the component variation is from  $-3\sigma$  to  $+3\sigma$ . Numbers for  $\sigma$  range from a low of 2% (for thin film resistors) to a high of 15% (advanced technology node transistors) for different components.

# 4. Defect filtering

This step involves choosing the simulation output by weeding out the outliers to build a good regression model. While it is important the signatures correlate well to the specification over the nominal component range, it is important that there is no correlation between the circuit specification and signature for the outlying component values. Defect filtering is a step that ensures any outliers in the circuit simulation are weeded out so that only the ideal circuit response is available for regression modeling between signature and the circuit specification. Popular defect filters use techniques from machine-learning for distinguishing the circuit-output [137, 139, 140] of a nominally good circuit (whose specification is within some predefined range) from a bad one.

#### 5. Building a regression model or a neural network classifier

Regression modeling is a step where a relational model relating the circuit signatures to the circuit specification that the signature seeks to replace is formulated. Multivariate Adaptive Regression Splines (MARS) [47] is a method that efficiently builds a regression model with only a small number of training samples - essentially pairs of specification and signature for different inputs applied to the circuit in question [59].

#### 6. Predicting specification from indirect measurements

Once an adequate regression model is available, the device-under-test (DUT) is applied with a stimulus to elicit a response, which is then used to predict the specification of

the circuit. If the regression model predicts a specification that is significantly deviant from the nominal range of acceptable specifications, then the DUT is classified as faulty; whereas if the deviation of the predicted specification is close to the boundary of the acceptable specification range, then the DUT can be either retested with actual specification measurements to minimize misclassification or the test procedure can rely solely on the indirect measurement (or signature), in which case there can be a defect level/yield loss penalty.

### 7. Improving the models in closed loop

The regression model built in the previous step can be continuously tuned to improve the correlation between test signature and specification. This is typically done by having an online training method that updates the regression model based on the actual specification measured on a small sample of training devices right off the production line.

#### 2.4 Conclusion

This chapter introduced the signature based test scheme and described the important constituent steps in this test methodology. In the next chapter we will examine polynomial coefficients as a circuit-test signature. We will demonstrate its use for fault detection and diagnosis on common analog circuits such as elliptic filter and low noise amplifier.

# Chapter 3

# Polynomial Coefficients as Test Signatures

### 3.1 Introduction

An analog circuit is called either linear or non-linear based on the type of input-output behavior it displays [38, 68]. Linear circuits preserve linearity and homogeneity of output with the input, and can be described by a linear constant coefficient differential equation [27]. Typically, in the time domain, the output y(t) may be expressed as a function of input x(t), as follows:

$$\sum_{m=1}^{M} a_m \frac{d^m y}{dt^m} + a_0 y = \sum_{n=1}^{N} b_n \frac{d^n x}{dt^n} + b_0 x \qquad (M > N)$$

(3.1)

where  $a_m, b_n \in \Re \ \forall \ m, n \in \mathbb{Z}$ . The general solution for (3.1) is of the form (3.2), where  $H(t) \in \Re$  is a real function of time t.

$$y(t) = H(t)x(t) \tag{3.2}$$

Linear circuits are mainly composed of passive components [38]. Typical examples include RC and LC ladder filters and resistive attenuators among others.

In case of non-linear circuits, coefficients  $a_m, b_n \, \forall m, n \text{ in } (3.1)$  are functions of x and a general solution in time domain for such circuits can be expressed as in (3.3), where  $H_n \, \forall n$  are real functions of t.

$$y(t) = \sum_{n=1}^{n=N} H_n(t)x^n(t)$$

(3.3)

Testing of linear circuits is well studied and several methods can be found in the literature [53, 85, 90, 93]. Savir and Guo [53] describe a method in which the circuit is modeled as a linear time-invariant (LTI) system. They obtain the transfer function of the circuit in

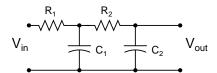

Figure 3.1: A second order low pass filter.

the frequency domain, which is of the following form:

$$H(s) = \frac{\sum_{i=0}^{M} a_i s^i}{\sum_{i=0}^{N} b_i s^i} \qquad (M < N)$$

(3.4)

The coefficients of the transfer function, i.e.,  $a_i$  and  $b_i$ , are all functions of circuit parameters and these are tracked to monitor drift in circuit parameters. The CUT is subjected to frequency rich input signals and the output voltage alone is observed. With these input-output pairs they estimate the transfer function coefficients of CUT. Next they compare these transfer function coefficient estimates with the ideal circuit transfer function coefficients, which are known a priori. The CUT is classified faulty if any of the estimated coefficients is beyond the tolerable range. For example, the circuit shown in Figure 3.1 is a second order low pass filter and has a transfer function given below:

$$H(s) = \frac{1}{(R_1 R_2 C_1 C_2) s^2 + (R_1 C_1 + (R_1 + R_2) C_2) s + 1}$$

(3.5)

Clearly the coefficients of the transfer function,  $b_0 = 1$ ,  $b_1 = (R_1C_1 + (R_1 + R_2)C_2)$ ,  $b_2 = R_1R_2C_1C_2$ , are functions of circuit parameters  $R_1$ ,  $R_2$ ,  $C_1$ ,  $C_2$ . Assuming single parametric faults, they find the minimum drift in any of the circuit component values that will cause the coefficients  $b_1$  or  $b_2$  ( $b_0$  here is a constant) to drift outside a tolerance range. However, this method [53] necessarily needs the CUT to be linear, as a frequency domain transfer function is possible only for a LTI system.

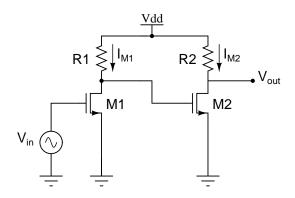

Figure 3.2: Cascade amplifier

Several methods have been proposed for parametric fault testing of non-linear circuits [6, 35, 37, 40, 44, 52, 75, 99]. A prominent method in the industry is the I<sub>DDO</sub> testing where quiescent current from the supply rail is monitored and sizable deviations from its expected value are monitored. However, this requires augmentation of the CUT. For example, in the simplest case a regulator supplying power to any sizable circuit has to be augmented with a current sensing resistor and an ADC (for digital output). Subsequently, analysis is performed on the sensed current.  $I_{DDQ}$  is found suitable only for catastrophic faults as the current drawn from the supply may be distinguishable when there is some "large enough" fault to change the quiescent current by a distinguishable amount. For example, with resistor  $R_2$  being open in Figure 3.2, the current drawn from supply can change by 50%of its nominal quiescent value. Such faults can typically be found by monitoring  $I_{DDQ}$  using a current sensor. However, parametric deviations, say, less than 10% from their nominal value cannot be observed using this scheme. This is especially so for the very deep submicron circuits where the leakage currents can be comparable to the defect induced current [45]. It is therefore useful to develop a method to detect parametric faults while testing with less circuit augmentation.

To address the issue of parametric deviation, we would typically need more observables to have an idea about the parametric drift in circuit parameters. This would mean an increase in the complexity of the sensing circuit. However, we would also want minimal augmentation to tap any of the internal circuit nodes or currents. To overcome these seemingly contrasting requirements the method intended should have some way of "seeing through" the circuit with only the outputs and inputs at its disposal. References [53, 93] give such strategies for linear circuits as described earlier.

To extend this idea to general non-linear circuits we adopt a strategy where we express the function of the circuit as a polynomial using a Taylor series expansion [72] in terms of input voltage  $v_{in}$ , about the point  $v_{in} = 0$  as follows:

$$v_{out} = f(v_{in}) = f(0) + \frac{f'(0)}{1!}v_{in} + \frac{f''(0)}{2!}v_{in}^2 + \frac{f'''(0)}{3!}v_{in}^3 + \cdots + \frac{f^{(n)}(0)}{n!}v_{in}^n + \cdots$$

(3.6)

where f(x) is a real function of x.

This method is very general as any analog circuit can be tested using this model. The technique applies equally well to linear circuits, which are a subclass of the general non-linear circuits considered in this paper. The accuracy, resolution and observability of faults uncovered depends on the degree of expansion of the coefficients in (3.7). Ignoring the higher order terms in (3.6), we can expand  $v_{out}$  up to the  $n^{th}$  power of  $v_{in}$ , which gives us the approximation in (3.7). In order to increase the available observables to better track down parametric faults we can expand  $v_{out}$  at multiple frequencies. Thus, we will have  $m \times (n+1)$  observables where m is the number of tones (frequencies) including DC at which  $v_{out}$  is expanded and n is the degree of expansion [55]:

$$v_{out} = a_0 + a_1 v_{in} + a_2 v_{in}^2 + \dots + a_n v_{in}^n$$

(3.7)

where  $a_0, a_1, a_2, \ldots, a_n$  are all real functions of circuit parameters  $p_k \forall k$ .

A special case of DC test, that detects a subset of faults, was given in a recent paper [125]. Further, we assume that normal parameter variations (normal drift) in a good circuit are within a fraction  $\alpha$  of their nominal value, where  $\alpha \ll 1$ . That is, every parameter  $p_i$  is allowed to vary within the range  $p_{k,nom}(1-\alpha) < p_k < p_{k,nom}(1+\alpha) \ \forall k$ , where  $p_{k,nom}$  is the nominal value of parameter  $p_k$ . Whenever one or more of the coefficient values slip outside its individual hypercube we get a different set of coefficients reflecting a detectable fault. Therefore, equation (3.8) describes the hypercube for all parameters that correspond to either good machine values or undetectable parametric faults [35, 53, 99]:

$$a_{i,\min} < a_i < a_{i,\max} \quad \forall i, \quad 0 \le i \le n \tag{3.8}$$